CD AUTO CHANGER

KDC-C465/Y

© 1999-12 PRINTED IN JAPAN

B51-7555-00(S) 3124

SERVICE MANUAL

The MECHANISM OPERATION DESCRIPTION is same as model KDC-C660.

Please refer to the service manual of model KDC-C660 (B51-7105-00).

Panel

(A64-2003-01):K2, E2

(A64-2011-01):E3

Dressing panel

(A21-3533-02):K2, E2

(A21-3532-12):E3

Metallic cabinet

(A01-2654-01)

When transporting these models, always attach CAUTION CARD

and STEPPED SCREW (for transportation).

CAUTION CARD

:B58127504

STEPPED SCREW

:N09418625

Service jig

Parts No.

For initial position setting

W05-0635-00

Dressing panel

(A21-3531-02):K2, E2

(A21-3530-12):E3

Holder assy (MAGAZINE)

(J19-4687-32)

Screw set

(N99-1645-15)

Bracket (R)

(J19-4715-13)

Bracket (L)

(J19-4713-13)

Blind plate

(F19-1303-04)

Cord with plug

(E30-4138-05)

KDC-C465/Y

2

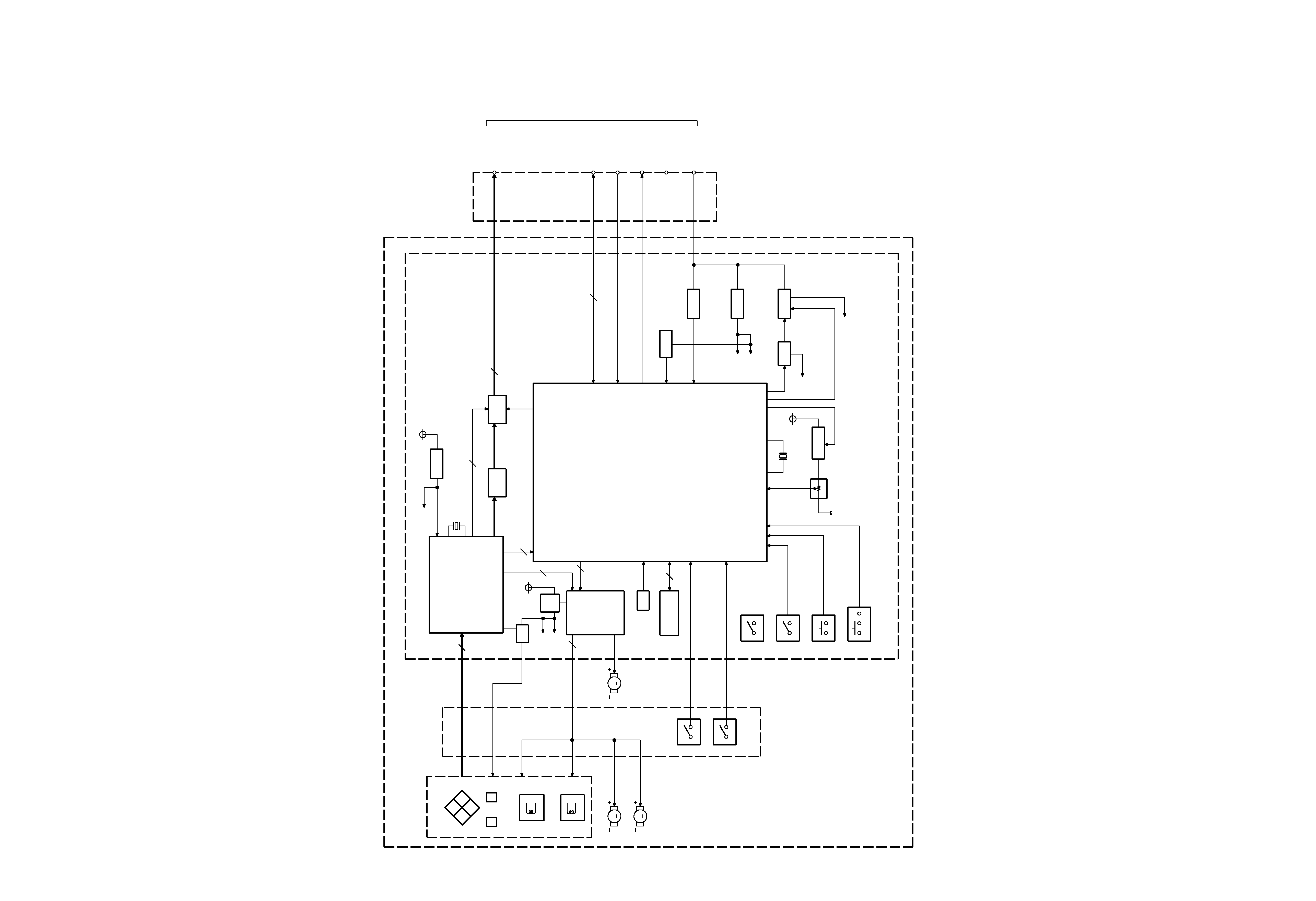

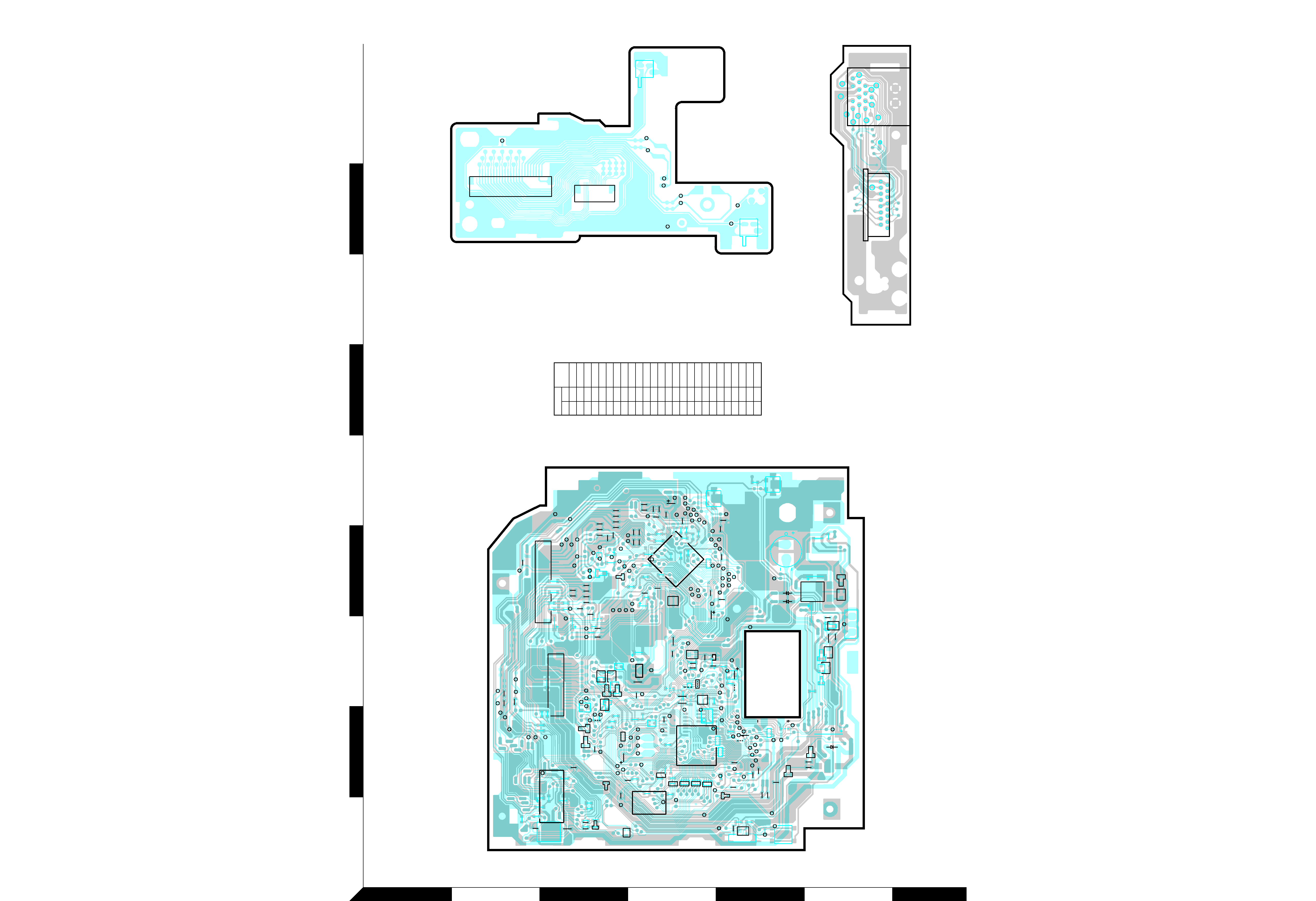

BLOCK DIAGRAM

M5V1

LIM

SW

L.P

.S

.

S4

COMM

SW

S2

EJ

SW

S3

ARM

SW

12.5MHz

A

VREF0

X2

SPINDLE

PD

SLED

LOE

SW

TR

COIL

FO

COIL

E

D

B

AC

M

OTO

R

DRIVER

BTL

&

DC

ELEV

A

T

OR

EEPR

OM

S-24C01B

HO

T

TEXT

DECODER

&

APC

SD5V

Q1

S8V

LA6556

Q9

UPD784214GC-062-8EU

SYSTEM

u-COM

IC7

IC1

RF

AMP

&

SER

V

O

DSP

&

16.93MHz

X1

P

ON

Q10

7V/9V

M5V1

M5V2

RESET

IC9

Q15,16

8V

A

V

R

Q20

Q21,22

B

U

.DET

5V

A

V

R

B

U14V

D

A5V

MUTE

5VREG

S8V

CH

CON

CH

RST

CH

MUTE

5L

I/F

A

UDIO

OUT

T0

IC8

7

4

5

8

2

5

Q6-8

IC4

IC5

AV

R

S5V

13

2

S8V

Q12

S1

MG

SW

3

HEAD

UNIT

M

MM

SA5V

UPD63711GC

D/A

CONVER

TER

&

SCF

OBIT

MUTE

Q4,5

F

KDC-C465/Y

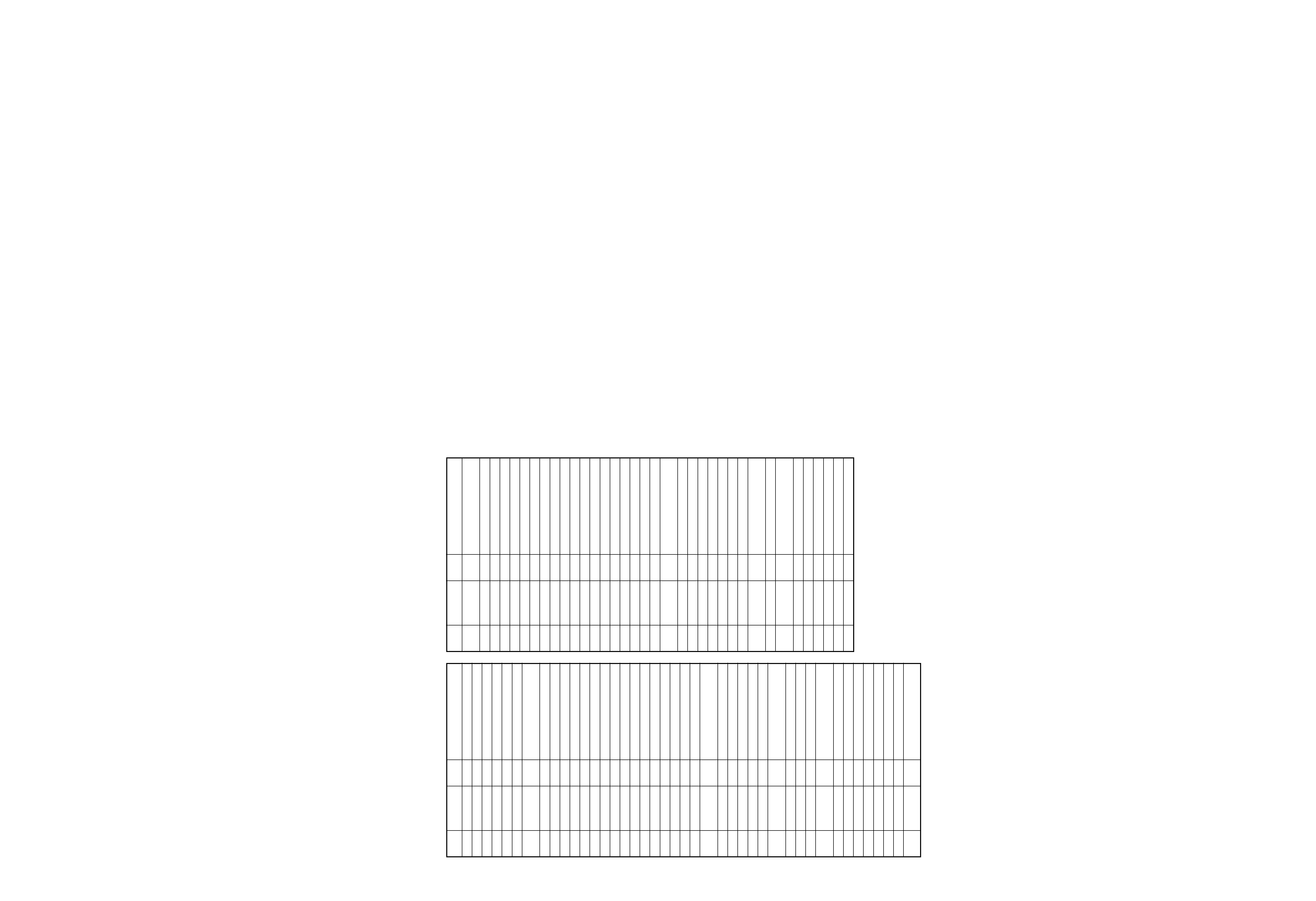

MICROCOMPUTER'S DESCRIPTION

ADJUSTMENT

3

4

KDC-C465/Y

System

µ-com : UPD784214GC (X32- : IC7)

qTerminal description

1

TOUT

O

Test output.

2

TSTB

O

Text data strobe signal.

3

-

O

NC.

4

FOK

I

H: Focusing OK. L: Focusing NG.

5

X OFF

O

H: Servo IC oscillation OFF.

6

RST

O

L: Servo IC reset.

7AO

O

H: Parameter setting.

L: Address register setting.

8

STB

O

L: Data latch.

9

VDD

Power supply connection.

10

X2

-

Oscillator.

11

X1

I

Oscillator.

12

VSS

I

GND.

13

XT2

-

NC.

14

XT1

GND.

15

RESET

I

L: Reset.

16

BSY

17

MGSW

I

H: Holder IN. L: Holder OUT.

18

EJSW

I

H: Eject.

19

COMMSW

I

H: New. L: Old.

20

PACK

I

Text data pack sync signal.

21

CHCON

I

Changer control.

22

BUDET

I

B-U detection.

23

AVDD

I

A/D converter power supply.

24

AVREF

I

A/D converter reference

voltage.

25

HOT

I

High temperature detection.

26

LPS

I

Position detection.

27

LOESW

I

L: Loading completed.

28

LIMSW

I

L: PU limit switch ON.

29

TOFF

I

Tracking off mode.

30

ADJSEL

I

H: Servo Adjustment OFF.

L: Servo Adjustment ON.

31

TBANK

I

H: Gain UP. L: Normal.

32

SIM3

33

AVSS

GND.

34

LPSCO

O

A/D converter power supply.

H: OFF.

35

AMUTE

O

L: Muting ON.

36

AVREF1

A/D converter power supply.

37

SDI

I

Servo data input.

38

SDO

O

Servo data output.

39

SCK

O

Servo clock output.

40

DATAH

I

Data input from H/U.

41

DATAC

O

Data output to H/U.

42

HCLK

I/O

H: Clock input.

L: Clock output.

Pin No.

Pin Name

I/O

Description

43

REQC

O

Communication request to

H/U.

44

CHMUTE

O

L: Muting ON.

45

TSO

O

Text data output.

46

TSI

I

Text data input.

47

TSCK

O

Text clock output.

48~55

A0~A7

O

S-RAM address setting.

56~63

D0~D7

I/O

S-RAM data input/output.

64~68

A8~A12

O

S-RAM address setting.

69~71

A13~A15

O

S-RAM enable control.

72

VSS

GND.

73, 74

A16, A17

O

S-RAM enable control.

75

RAMOK

O

H: OK.

76

ELVADJ

I

L: Adjustment mode.

77

RD

O

S-RAM read control.

78

WR

O

S-RAM write control.

79

WAIT

I

Wait during S-RAM access.

80

ASTB

O

NC.

81

VDD

Power supply connection.

82

RAMTEST

I

H: S-RAM check mode.

83

REQH

I

Communication request from

H/U.

84

SP/LO+

O

Spindle/Loading + control.

85

SP/LO-

O

Spindle/Loading - control.

86

ELV+

O

Mechanism UP/DOWN control.

87

ELV-

O

Mechanism UP/DOWN control.

88

SIM1

I

L: Text. H: No Text.

89

SEARCH

O

H: Play. L: Search.

90, 91

TEST1, 2

I

L: Normal. H: Test.

92

8V/7V

O

H: 7 V. L: 8 V (Servo power

supply).

93

SLG

I

H: +3 dB. L: 0 dB (Sled gain).

94

TEST/VPP

I

L: Flash ROM program mode

OFF.

95

SRVSEL

I

H: Servo mode.

96

SLNSA

I

L: Sled non-sensible area ON.

97

SDA

I/O

EEPROM data input/output.

98

SCL

O

EEPROM clock output.

99

PON

O

L: Power ON.

100

ARMSW

I

H: Arm switch ON.

Pin No.

Pin Name

I/O

Description

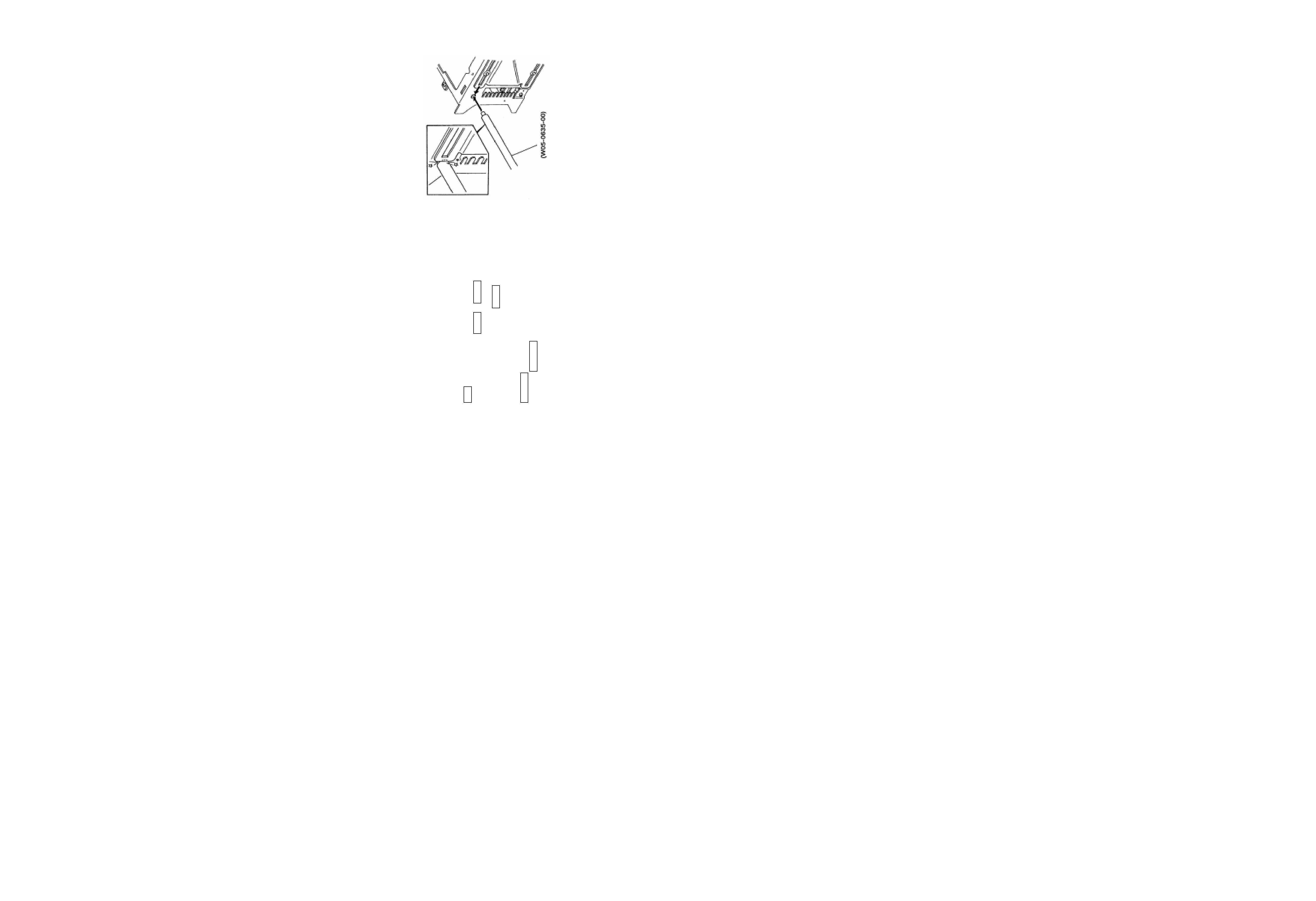

LPS initial position adjustment procedure

Connect the changer to the H/U. While holding the

magazine eject button of the changer, press the reset button

of the H/U and, in about 1 second, release the magazine

eject button. Press the CD button of the H/U to enter the

E-88 mode. Move the mechanism deck to around the 1st

stage by pressing the DISC- or DISC+ button.

Insert the adjustment tool into the tool hole on the changer

mechanism. Then press the DISC+ button to move the

mechanism deck until the mechanism's slider hits the

adjustment tool. When the motor locks (stops) press the

REPEAT key of the H/U.

When the REPEAT key is pressed, the mechanism moves

automatically to the 1st stage and the initial position

adjustment completes. (The data is written in the E2PROM

at this time.)

KDC-C465/Y

MICROCOMPUTER'S DESCRIPTION

ADJUSTMENT

3

4

KDC-C465/Y

System

µ-com : UPD784214GC (X32- : IC7)

qTerminal description

1

TOUT

O

Test output.

2

TSTB

O

Text data strobe signal.

3

-

O

NC.

4

FOK

I

H: Focusing OK. L: Focusing NG.

5

X OFF

O

H: Servo IC oscillation OFF.

6

RST

O

L: Servo IC reset.

7AO

O

H: Parameter setting.

L: Address register setting.

8

STB

O

L: Data latch.

9

VDD

Power supply connection.

10

X2

-

Oscillator.

11

X1

I

Oscillator.

12

VSS

I

GND.

13

XT2

-

NC.

14

XT1

GND.

15

RESET

I

L: Reset.

16

BSY

17

MGSW

I

H: Holder IN. L: Holder OUT.

18

EJSW

I

H: Eject.

19

COMMSW

I

H: New. L: Old.

20

PACK

I

Text data pack sync signal.

21

CHCON

I

Changer control.

22

BUDET

I

B-U detection.

23

AVDD

I

A/D converter power supply.

24

AVREF

I

A/D converter reference

voltage.

25

HOT

I

High temperature detection.

26

LPS

I

Position detection.

27

LOESW

I

L: Loading completed.

28

LIMSW

I

L: PU limit switch ON.

29

TOFF

I

Tracking off mode.

30

ADJSEL

I

H: Servo Adjustment OFF.

L: Servo Adjustment ON.

31

TBANK

I

H: Gain UP. L: Normal.

32

SIM3

33

AVSS

GND.

34

LPSCO

O

A/D converter power supply.

H: OFF.

35

AMUTE

O

L: Muting ON.

36

AVREF1

A/D converter power supply.

37

SDI

I

Servo data input.

38

SDO

O

Servo data output.

39

SCK

O

Servo clock output.

40

DATAH

I

Data input from H/U.

41

DATAC

O

Data output to H/U.

42

HCLK

I/O

H: Clock input.

L: Clock output.

Pin No.

Pin Name

I/O

Description

43

REQC

O

Communication request to

H/U.

44

CHMUTE

O

L: Muting ON.

45

TSO

O

Text data output.

46

TSI

I

Text data input.

47

TSCK

O

Text clock output.

48~55

A0~A7

O

S-RAM address setting.

56~63

D0~D7

I/O

S-RAM data input/output.

64~68

A8~A12

O

S-RAM address setting.

69~71

A13~A15

O

S-RAM enable control.

72

VSS

GND.

73, 74

A16, A17

O

S-RAM enable control.

75

RAMOK

O

H: OK.

76

ELVADJ

I

L: Adjustment mode.

77

RD

O

S-RAM read control.

78

WR

O

S-RAM write control.

79

WAIT

I

Wait during S-RAM access.

80

ASTB

O

NC.

81

VDD

Power supply connection.

82

RAMTEST

I

H: S-RAM check mode.

83

REQH

I

Communication request from

H/U.

84

SP/LO+

O

Spindle/Loading + control.

85

SP/LO-

O

Spindle/Loading - control.

86

ELV+

O

Mechanism UP/DOWN control.

87

ELV-

O

Mechanism UP/DOWN control.

88

SIM1

I

L: Text. H: No Text.

89

SEARCH

O

H: Play. L: Search.

90, 91

TEST1, 2

I

L: Normal. H: Test.

92

8V/7V

O

H: 7 V. L: 8 V (Servo power

supply).

93

SLG

I

H: +3 dB. L: 0 dB (Sled gain).

94

TEST/VPP

I

L: Flash ROM program mode

OFF.

95

SRVSEL

I

H: Servo mode.

96

SLNSA

I

L: Sled non-sensible area ON.

97

SDA

I/O

EEPROM data input/output.

98

SCL

O

EEPROM clock output.

99

PON

O

L: Power ON.

100

ARMSW

I

H: Arm switch ON.

Pin No.

Pin Name

I/O

Description

LPS initial position adjustment procedure

Connect the changer to the H/U. While holding the

magazine eject button of the changer, press the reset button

of the H/U and, in about 1 second, release the magazine

eject button. Press the CD button of the H/U to enter the

E-88 mode. Move the mechanism deck to around the 1st

stage by pressing the DISC- or DISC+ button.

Insert the adjustment tool into the tool hole on the changer

mechanism. Then press the DISC+ button to move the

mechanism deck until the mechanism's slider hits the

adjustment tool. When the motor locks (stops) press the

REPEAT key of the H/U.

When the REPEAT key is pressed, the mechanism moves

automatically to the 1st stage and the initial position

adjustment completes. (The data is written in the E2PROM

at this time.)

A

B

C

D

E

F

G

I

H

1

2

3

4

5

6

7

5

6

PC BOARD (Component Side View)

C2

R8

R85

C300

R86

CP8

CP7

C14

C56

R191

C206

C202

C24

R135

R136

R137

S2

R138

C4

C62

R205

C73

CP16

C11

R19

R18C12

C59

C13

C66

R20

CP15

CP14

R142

C34

R140

R141

R143

R57

R112

C192

R71

C60

C55

R25

R161

R193

R26

C201

C21

R21

R22

CP17

R157

CP1

R80

R81

R82

R15

R93

C49

C67

S3

R32

R95

W9

R100

C204

C48

R58

C46

R75

R74

C47

R110

C23

R111

C205

R121

R60

R61

R190

R148

R108

R107

L1

R98

W12

R124

R101

R154

R153

R155

R156

W17

R149

C85

R150

R151

C64

S4

CP9

W16

C301

R50

R125

C194

C193

R194

R192

TH1

S1

E B

E

B

E

B

BE

B

E

BE

BE

E

B

EB

C

C

EC

B

4

C75

1

5

8

Q9

Q19

D14

D5

D20

D1

Q12

IC8

Q10

Q14

Q13

D4

Q1

Q5

Q4

Q15

C5

C6

C52

R152

R180

C180

C16

C190

C184

C15

R53

R54

CP11

CP10

CP6

CP5

CP12

R4

X1

R126

R6

R3

R7

R5

R10

R9

C7

R16

C8

R203

R202

R206

C9

C10

R181

C181

L2

R69

R134

R184

R113

W6

C17

C63

R123

C200

R67

R70

R122

C3

C203

W5

C72

R201

R78

R68

R102

R79

X2

W7

C68

R96

R97

C69

R99

W10

C70

C61

R77

R76

R83

R72

R73

R129

R182

C71

C182

R2

R1

C19

R84

R87

R162

CP3

W21

R106

R105

R139

R183

C183

E

B

B

E

B

E

E

B

E

B

BE

E

B

B

E

B

E

B

E

1

S8V

FCLK

FDATAO

1

FDATAI

HOT

12.5

FRESET

CHRST

TOFF

1

TE

SD

TD

MD

LOCK

SD5V

SBSY

SDGND

SLNSA

SRVSEL

VPP

SLG

AMUTE

REQC

DATAH

TBAL

FBAL

TSI

PACK

1

FE

SAGND

ASY

/TSTB

TOUT

TEVCA

EFM

8/7V

18

SGND

RF

SA5V

PUGND

VR

MGND

M5V1

M5V2

FVDD

FGND

TROFF

SL-

SL+

REQH

LPSCO

TSO

/TSCK

TSI

A

Vref0

SO

GND

LPS

ADJSEL

TBANK

RD

1

SPLOD-

COMMSW

RAMOK

RAMTEST

WR

TEST2

TEST1

SEARCH

SIM1

SCL

SDA

RESET

/XENB

TX

WDCK

EMPH

FLAG

RFCK

PLCK

C1D1

TBC

C2D2

C2D1

C1D2

/TSTB

ARMSW

DACO

ATEST

VCC

HOLD

IOP2-

IOP1+

PN

MIRR

SPLOD+

BUDET

ELVADJ

EJSW

PD

LD

Vref

ARF

CH MUTE

Rch

Lch

LIMSW

LOESW

A

C

B

D

/CHCON

/CE1

EL

VD-

EL

VD+

SEARCH

ELV+

SP-

SP+

T-

T+

F+

F-

/STB

A0

SO

/RST

FOK

E

SI

DA5V

DAGND

IG O

3TE

TSO

/TSCK

MGSW

F

/SCK

ELV-

PON

FD

1

36

19

16

23

7

8

21

22

28

25

26

50

51

75

76

100

1

2

4

3

25

26

50

51

75

76

100

MHz

E

B

Q21

Q22

D8

D10

IC1

IC7

D9

D11

D13

IC5

IC4

IC11

D16

D23

D24

Q16

Q17

Q18

Q11

CN2

Q7

Q6

D12

D7

Q8

Q20

D3

D15

D21

D22

Q31

IC9

CN1

X32-4660-00/4670-00 (J74-0966-01)

CD PLAYER UNIT (X32-4660-01)

SUB-CIRCUIT UNIT (X13-9730-00)

S2

S1

1

1

LIMSW

LOESW

8/12SW

MGND

SP-

SL-

SL+

SP+

BLA

CK

RED

18

16

CN1

CN2

X13-9730-00/9740-00 (J74-0987-01)

SUB-CIRCUIT UNIT (X13-9000-00)

CD PLAYER UNIT

(X32-4660-01)

Refer to the schematic diagram for the values of resistors and capacitors.

.

O

N

.

f

e

R

s

s

e

r

d

d

A

C

IQ

1D

4

4C

4

5A

3

7B

4

8B

4

9C

4

1D

3

4C

3

5C

3

6C

3

7C

3

8C

3

9A

3

0

1C

5

1

1C

4

2

1B

4

3

1C

3

4

1B

3

6

1C

6

7

1C

6

8

1C

6

9

1C

6

0

2A

5

1

2D

6

2

2D

6

1

3A

3

GND

A-GND

BU14V

REQH

RATAC

REQC

CH-CLK

DATAH

Lch

Rch

CH-MUTE

CH-RST

CH-CON

1

1

5

9

13

8

12

4

J1

2

15

CH1

16

(J74-0619-12)

X13-9000-00