NAME SET

DISP

ATT

B.S

S.A

DSP

AUD

EQ

PWR OFF

OPEN

CD EJECT

SRC

AM

FM

+

DISC

FNC

1 BNR

2 SCN

3 RDM

METAL

6 M.RDM

4 REP

5 D.SCN

DISP

ATT

S.A

DSP

EQ

SRC

AM

FM

+

1 BNR

2 SCN

3 RDM

6 M.RDM

4 REP

5 D.SCN

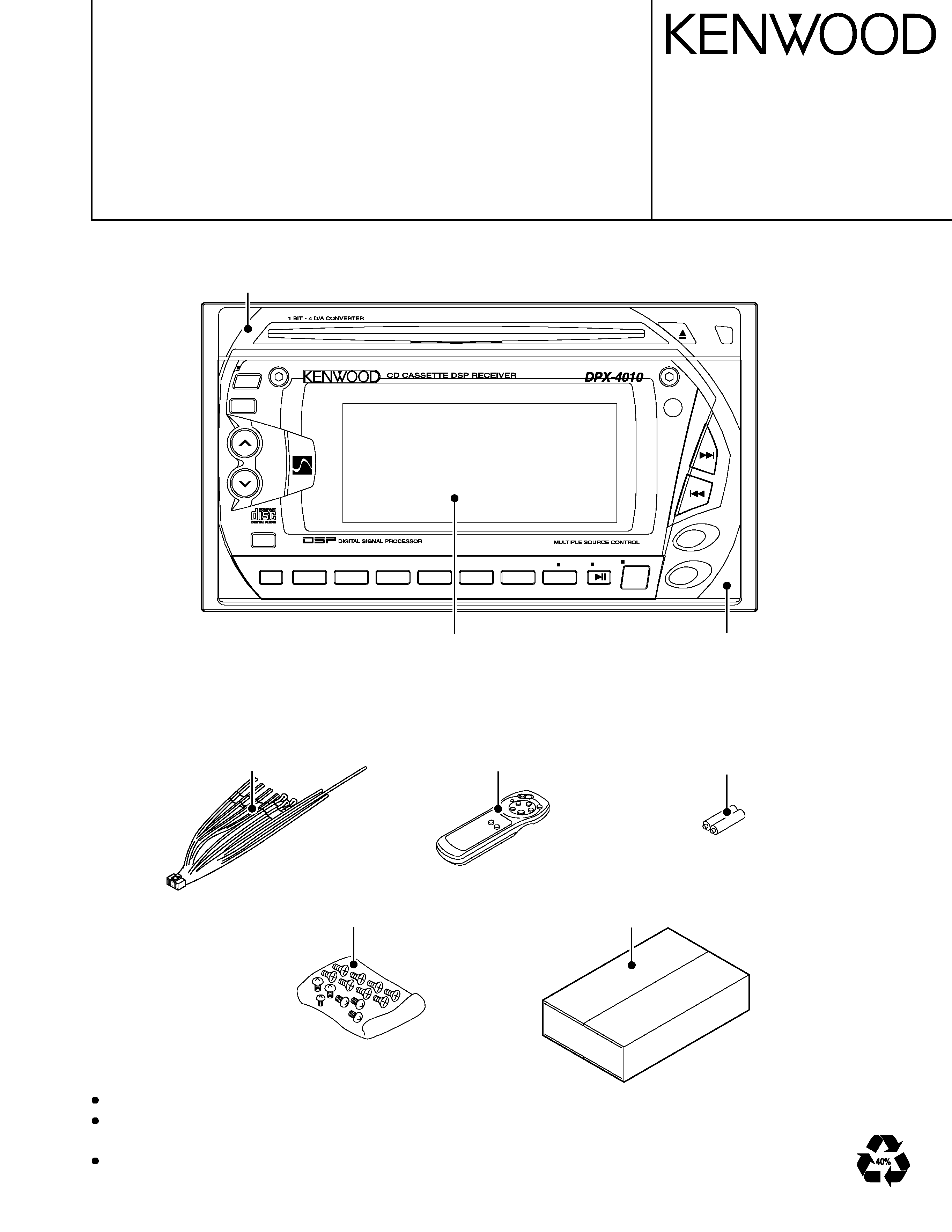

DPX-4010

DPX-4010/PH4

CD CASSETTE DSP RECEIVER

SERVICE MANUAL

© 2000-7 PRINTED IN JAPAN

B51-7656-00 (N) 1694

Front glass assy

(B10-4041-08) : K type or M type

(B10-4043-08) : PH4 type

Front panel assy

(A64-2284-08) : K type

(A64-2285-08) : M type or PH4 type

Sub panel

(A22-2880-08)

DC cord assy

(E30-4860-08)

DPX-4010/PH4 is philippines HONDA genuine model.

CD mechanism operation description is please refer to the

service manual KDC-5007/5008 (B51-7090-00).

Cassette mechanism operation description is please refer to the

service manual D40-1122-05 (B51-7452-00).

Remote controller assy

(A70-0883-05)

Screw set

(N99-1671-08)

HONDA attach kit

(J21-9578-05) : K type or M type

(J21-9617-05) : PH4 type

Size AAA battery

(Not supplied)

2

LPF

AM/FM

TUNER

PLL

LC72135M

BA3131FS

SELECT

OR

IC380

CD

MECHA

DXM-1051

TN-708

C

MECHA

IC200

CXA2560Q

MO

T

OR

DR

V

BA6219BFP-Y

EQ/NR//MS

IC250

TD

A7420

IC300

E-V

OL

BAL

VO

L

FR

ONT

REAR

BA3129F

IC351

SELECT

OR

M65849BFP

DSP

IC820

5L-B

US

CD-CH

IC1

MN101C15

SYSTEM

u-COM

PO

WER-AMP

IC500

TD

A7386

IC350

NJM4565M-D

B

UFF

BA3129F

SELECT

OR

IC351

REAR

SP

OUT

SP

OUT

FR

ONT

FR

ONT

PRE

OUT

PRE

OUT

REAR/NON-F

AD

IC851

NJM4565M-D

ALC

M61506FP

BPF

IC980

MN101C10

PNL

u-COM

IC900

VFD

KEY

REMOCON

RS-21

IC150

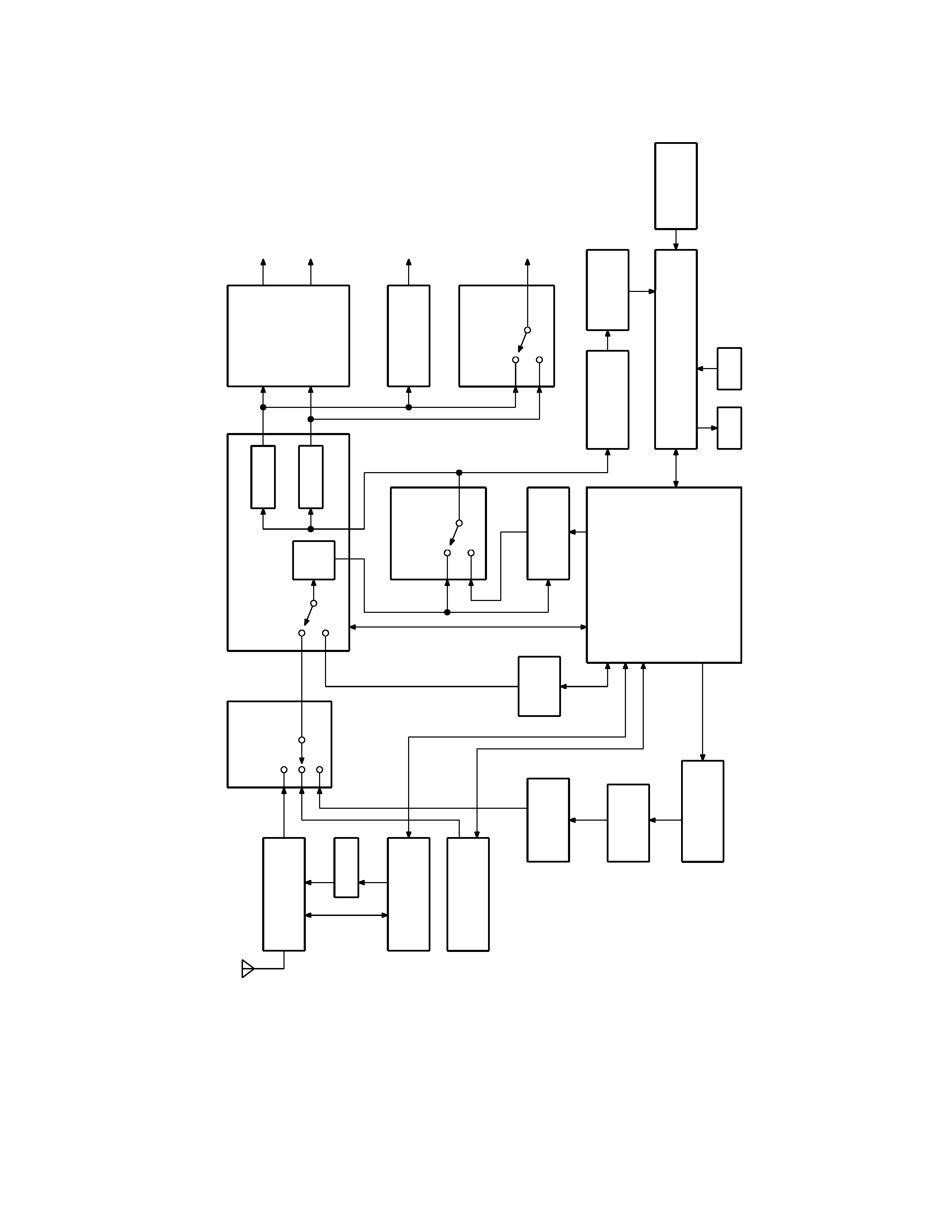

BLOCK DIAGRAM

DPX-4010,4010/PH4

3

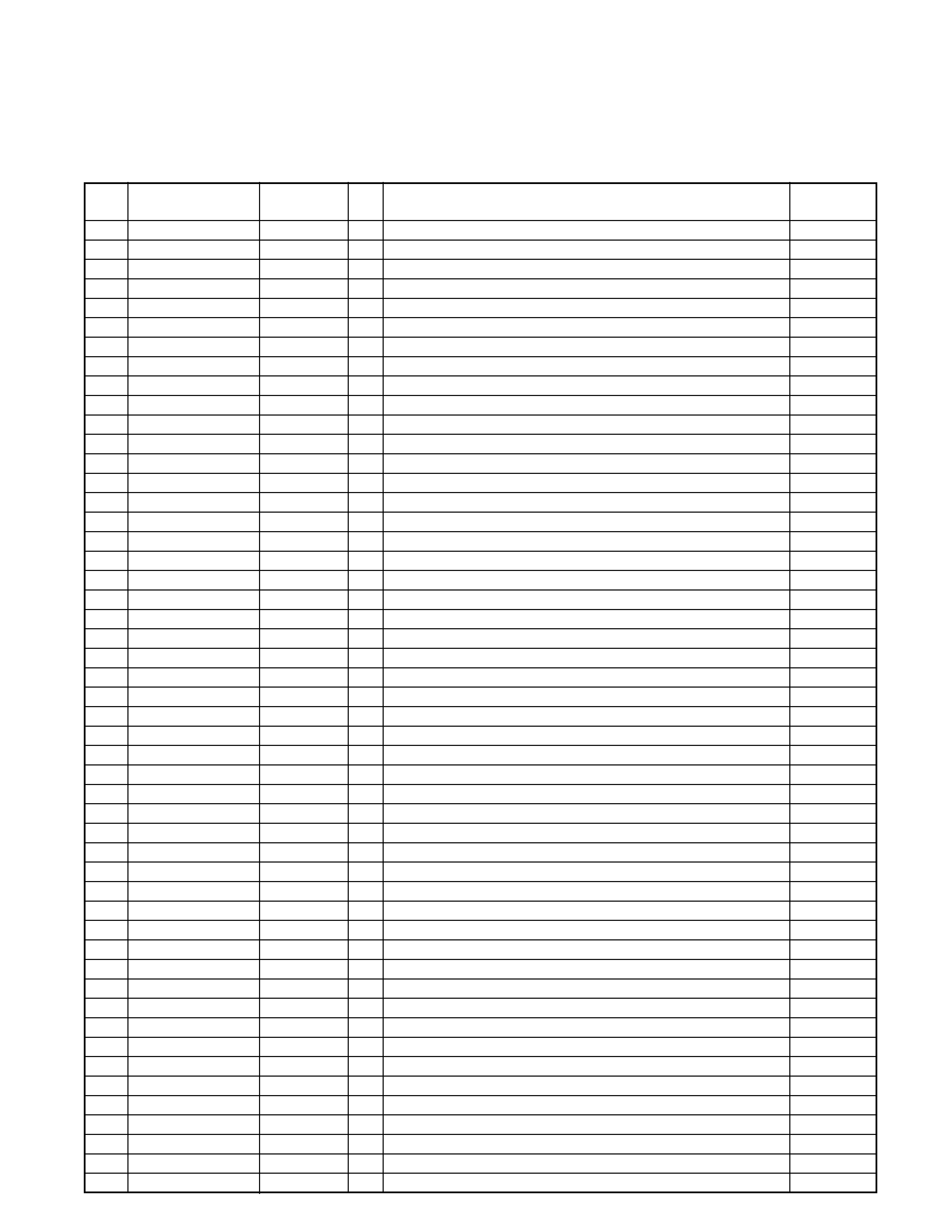

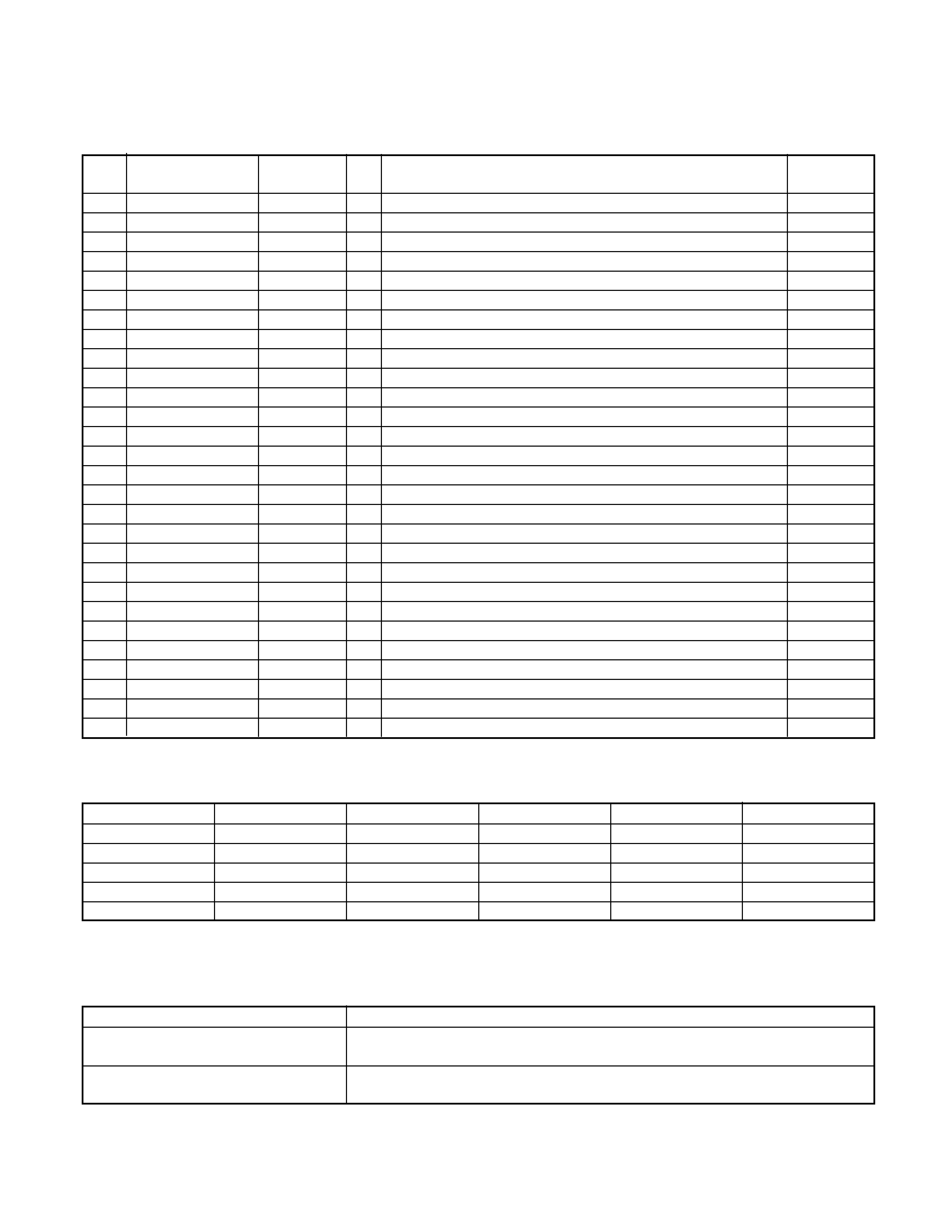

System Microcomputer MS101C15FCJ (IC1: Main PWB Unit)

Pin No.

Pin Name

Signal Name

I/O

Purpose/Description

Normal Operation

Level

1

VREF ()

Connected to GND

2

PA0/AN0

CD_EJ

I

CD/EJ_SW detection terminal [H: Normal. L: Eject]

L (a)

3

PA1/AN1

TYPE

I

Destination type selection input [H: J Type. M: K Type. L: M Type]

4

PA2/AN2

REEL_S

I

REV reel pulse detection terminal

H/L

5

PA3/AN3

REEL_T

I

FWD reel pulse detection terminal

H/L

6

PA4/AN4

AM_SD

I

AM SD input [H: Station detected. L: Station not detected]

H (a)

7

PA5/AN5

FM_SA

I

FM SD input [H: Station detected. L: Station not detected]

H (a)

8

PA6/AN6/

NC

I

9

PA7/AN7

SMALL

I

SMALL detection input [H: SMALL off. L: SMALL on]

L (a)

10

VREF (+)

Connected to BU 5 V

11

Vdd

Connected to Vdd

12

OSC2

X'Tal (8. 38)

X'tal (connected to 8.38 MHz)

13

OSC1

X'Tal (8. 38)

X'tal (connected to 8.38 MHz)

14

Vss

Connected to GND

15

Xl

Connected to GND

16

XO

Open

17

MMOD

Connected to GND

18

P00/SBO0/TXD

C_MAIN_M

O

C-mechanism motor control [H: ON. L: OFF]

H (a)

19

P01/SBI0/RXD

INPUT_SEL1

O

E_VOL input switching control (in combination with pin 20)

H/L

20

P02/SBT0

INPUT_SEL2

O

[HL: CD. LH: Tape. LL: Tuner]

H/L

21

P03/SBO1

CH_DATAH

O

Data output to CD-CH

H/L

22

P04/SBI1

CH_DATAC

I

Data input from CD-CH

H/L

23

P05/SBT1

CH_CHCLK

I/O

Previous bus: Data input from CD-CH. New bus: Data output to CD-CH.

H/L

24

P06/BUZZER/DK

BEEP

O

Beep output [Permanently L]

L

25

P27/RESET

RESET

I

System reset [H: Operation. L: Reset]

L (a)

26

P10/TM010/RMOUT

CH_REQH

O

Send request output to CD-CH

L (a)

27

P11/TM1IO

CH_CHCON

O

CD-CH operation control

H (a)

28

P12/TM2IO

CH_CH1/2

O

CD-CH 1/2 switching output

29

P13/TM3IO

PNL_OPEN

I

Panel open detection [H: Closed. L: Open]

L (a)

30

P14/TM4IO

TP

O

Test point (Valid only in test mode). [Permanently L]

L

31

P20/IRQ0

BU_DET

I

Back_Up detection input [H: Power down. L: Normal]

H (a)

32

P21/IRQ1/SENS

CH_REQC

I

Send request input from CD-CH

L (a)

33

P22/IRQ2

PN_SC_REQ

I

Send request input from PNL_

µCOM

H (a)

34

P23/IRQ3

TYPE2

I

Destination type selection input (for genuine model)

35

P24/IRQ4

ACC_DET

I

Acc detection input [H: Acc OFF. L: Acc ON]

H (a)

36

P30/SBO2

CD_DATA

I/O

Data input/output from/to CD mechanism

H/L

37

P31/SBI2

NC

I

Not used (Open)

38

P32/SBT2

CD_CDK

O

CLK output to CD mechanism

H/L

39

P33/BR

C_SUB_M+

O

C-mechanism loading motor control

H (a)

40

P34/BT

C_SUB_M

O

C-mechanism loading motor control

H (a)

41

P35/LDDMA

C_MSC

O

Blank detection mode control [H: G2 (in play mode). L: G1 (in FF mode)]

H/L

42

P36/STDMA

C_NR

O

Dolby ON/OFF control

H (a)

43

P37/DKDMA

C_MS_IN

I

Blank pulse detection input

H/L

44

P40/KEY0

C_MTL

O

Metal ON/OFF control.

H (a)

45

P41/KEY1

C_MODE2

I

Sub-motor control terminal 2

H/L

46

P42/KEY2

C_MODE3

I

Sub-motor control terminal 3 (cassette pack IN detection terminal)

H/L

47

P43/KEY3

C_MODE1

I

Sub-motor control terminal 1

H/L

48

P44/KEY4

DSP_DATA

O

DATA output to DSP

H/L

49

P45/KEY5

DSP_CLK

O

CLK output to DSP

H/L

50

P46/KEY6

DSP_STB

O

LATCH output to DSP

H/L

MICROCOMPUTER'S TERMINAL DESCRIPTION

DPX-4010,4010/PH4

4

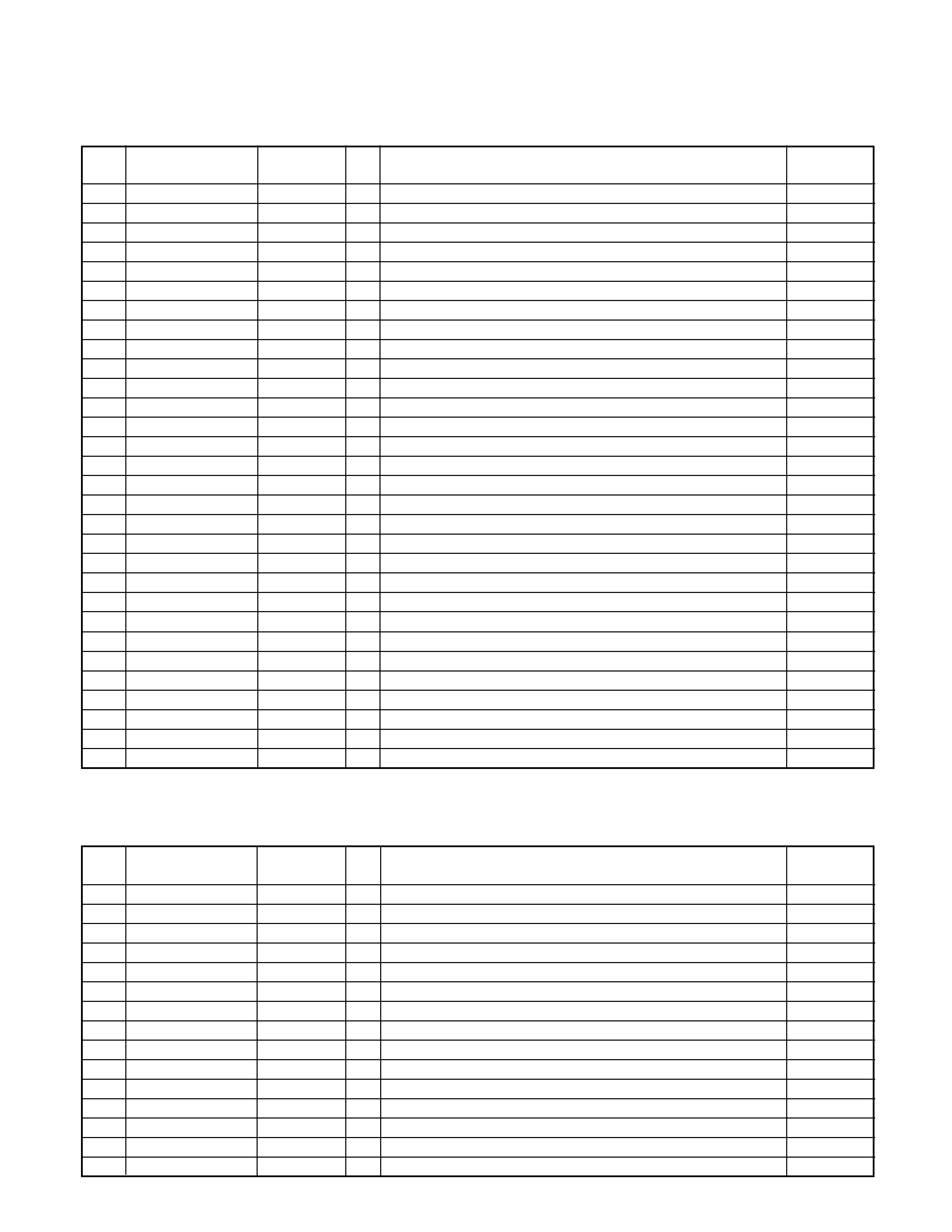

Pin No.

Pin Name

Signal Name

I/O

Purpose/Description

Normal Operation

Level

51

P47/KEY7

NF_MUTE

O

Muting of N-F when N-F is selected [H: Muting. L: Normal]

H (a)

52

P50/WE

AUDIO1

O

LINE OUT switching [H: FRONT. L: REAR]

H (a)

53

P51/RE

DSP_CONT

O

DSP ON/OFF control [L: DSP OFF (bypass). H: DSP ON]

H (a)

54

P52/CS

MUTE

O

AUDIO_MUTE output [H: Muting ON. L: Muting OFF]

H (a)

55

P53/A16

P_ON

O

Internal power control [H: ON. L: OFF]

H (a)

56

P54/A17

P_CON

O

External power control [H: ON. L: OFF]

H (a)

57

P60/A0

EVOL_DATA

I/O

DATA input/output from/to E_VOL (TDA7400)

H/L

58

P61/A1

EVOL_CLK

O

CLK output to E_VOL (TDA7400)

H/L

59

P62/A2

CD_SW1

I

Input from CDSW1 (Loading start SW)

L (a)

60

P63/A3

CD_SW2

I

Input from CDSW2 (12 cm disc detection SW)

L (a)

61

P64/A4

CD_SW3

I

Input from CDSW3 (Down & limit SW)

L (a)

62

P65/A5

CD_LO/EJ

I/O

CD mechanism loading motor control (LO/EJ) [H: Load. L: Eject]

H (a)

63

P66/A6

CD_LMON

O

CD mechanism loading motor control (ON/OFF) [H: Stop. L: Operate]

H (a)

64

P67/A7

C_F/R

O

Head switching control [H: Reverse. L: Forward]

H/L

65

P70/A8

CD_MSTOP

O

CD mechanism emergency stop output

L (a)

66

P71/A9

CD_MRST

O

CD mechanism reset output

L (a)

67

P72/A10

CD_MUTE

I

Muting input from CD mechanism

L (a)

68

P73/A11

P_ANT

O

POWER_ANT control [H: Radio mode. L: Other mode]

H (a)

69

P74/A12

PLL_CE

O

CE selection to LC72135M

H (a)

70

P75/A13

PLL_DO

O

DATA output to LC72135M

H/L

71

P76/A14

PLL_CLK

O

CLK output to LC72135M

H/L

72

P77/A15

PLL_CI

I

DATA input from LC72135M

H/L

73

P87/LED7/D7

SW40

O

VFD_Vdd2 control [H: Vdd2 ON. L: Vdd2 OFF]

H (a)

74

P86/LED6/D6

ILL_CON

O

Button illumination control [H: Illumination ON. L: Illumination OFF]

H (a)

75

P85/LED5/D5

PWIC_STBY

O

Power IC standby control [H: AMP ON. L: AMP OFF]

H (a)

76

P84/LED4/D4

PN_MC_REQ

O

Send request output to PNL_

µCOM

H (a)

77

P83/LED3/D3

PN_SC_CON

O

Operation control output to PNL_

µCOM

H (a)

78

P83/LED2/D2

PN_MC_DATA

O

DATA output to PNL_

µCOM

H/L

79

P81/LED1/D1

PN_SC_DATA

I

DATA input from PNL_

µCOM

H/L

80

P80/LED0/D0

PN_MC_CLK

O

CLK output to PNL_

µCOM

H/L

Level: High level (active)

H (a), Low level (active) L (a)

Panel Microcomputer MN101C10AAK (IC900: Combination PWB Unit)

Pin No.

Pin Name

Signal Name

I/O

Purpose/Description

Normal Operation

Level

1~5

NC (GND)

I

Not used (GND)

L

6

VREF+

VREF+

I

A/D conver ter reference voltage input terminal

7

VDD

VDD

Positive power supply terminal

8

OSC2

OSC2

Main clock connection (8.38 MHz)

9

OSC1

OSC1

Main clock connection (8.38 MHz)

10

VSS

VSS

Connected to GND

11

XI

XI

I

Connected to GND

L

12

XO

XO

O

Not used (Open)

13

MMOD

MMOD

I

Connected to GND

L

14

P00/SBO0/TXD

PN_SC_DATA

O

System control communication, data output terminal

H/L

15

P01/SBI0/RXD

PN_MC_DATA

I

System control communication, data input terminal

H/L

16

P02/SBT0

PN_MC_CLK

I

System control communication, clock input terminal

H/L

17

P03/SBO1

VFD_DATA

O

VFD driver data output

H/L

18

P04/SBI1

NC

O

Not used (Open)

L

19

P05/SBT1

VFD_CLK

O

VFD driver clock output

H/L

MICROCOMPUTER'S TERMINAL DESCRIPTION

DPX-4010,4010/PH4

5

Pin No.

Pin Name

Signal Name

I/O

Purpose/Description

Normal Operation

Level

20

P06/BUZ/DK

VFD_STB

O

VFD driver latch output

H/L

21

P27/RST

RST

I

Microcomputer reset

L (a)

22

P10/TM0IO/RMO

VFD_BLK

O

VFD driver blank output

L (a)

23~25

NC

O

Not used (Open)

L

26

P14/TM4IO

PN_SC_REQ

O

System control communication, send request output

H (a)

27

P20/IRQ0

PN_MC_REQ

I

System control communication, receive request input

H (a)

28

P21/IRQ/SENS

PN_SC_CON

I

System control communication, panel operation control

H (a)

29

P22/IRQ2

REMOCON

I

Remote control signal input

H/L

30

P23/IRQ3

KR0

I

Key return signal input 0

H/L

31

P24/IRQ4

KR1

I

Key return signal input 1

H/L

32

P50/WE

KR2

I

Key return signal input 2

H/L

33

P51/RE

KR3

I

Key return signal input 3

H/L

34

P52/CS

KR4

I

Key return signal input 4

H/L

35

P53/A16

NC

O

Not used (Open)

L

36

P54/A17

NC

O

Not used (Open)

L

37

P60/A0

KS0

O

Key scan signal output 0

H/L

38

P61/A1

KS1

O

Key scan signal output 1

H/L

39

P62/A2

KS2

O

Key scan signal output 2

H/L

40

P63/A3

KS3

O

Key scan signal output 3

H/L

41

P64/A4

KS4

O

Key scan signal output 4

H/L

42~56

NC

O

Not used (Open)

L

57

P83/D3/LED3

ENB

O

Peak hold IC output switching enable

H (a)

58

P82/D2/LED2

SEL_C

O

Peak hold IC output setting change

H (a)

59

P81/D1/LED1

SEL_B

O

Peak hold IC output setting change

H (a)

60

P80/D0/LED0

SEL_A

O

Peak hold IC output setting change

H (a)

61

VREF

VREF

I

Connected to GND

L

62

PA0/AN0

PH_IN

I

Peak hold input terminal

A

63,64

NC (GND)

I

Not used (GND)

L

Level: High level (active)

H (a), Low level (active) L (a)

Key Matrix Table

KS0

KS1

KS2

KS3

KS4

KR0

SRC

M1

M2

SA

PAUSE

KR1

CREJ

M3

M4

FM

KR2

M5

M6

AM

KR3

DSP

ATT

VOL (+)

TUN (+)

KR4

EQ

DISP

VOL ()

TUN ()

Line valid when OFF

*

CD-EJ is detected by the System Controller.

Allocation of Multi-press Keys

Key Allocation

Function

While ALL OFF,

Start the unit in test mode.

DSP + EQ + SRC

While ALL OFF,

Span switching (Valid only with K and M Types)

M1 + M5 + SRC

AM: [9K/10K]. FM: [50K/200K]

MICROCOMPUTER'S TERMINAL DESCRIPTION

DPX-4010,4010/PH4