CAUTION:

Before servicing this chassis, it is important that the service technician read the "Safety

Precautions" and "Product Safety Notices" in this service manual.

ATTENTION:

Avant d'effectuer l'entretien du châassis, le technicien doit lire les «Précautions de sécurité»

et les «Notices de sécurité du produit» présentés dans le présent manuel.

VORSICHT:

Vor Öffnen des Gehäuses hat der Service-Ingenieur die ,,Sicherheitshinweise" und ,,Hinweise

zur Produktsicherheit" in diesem Wartungshandbuch zu lesen.

SERVICE MANUAL

MANUEL D'ENTRETIEN

WARTUNGSHANDBUCH

Data

contained

within

this

Service

manual is subject to alteration for

improvement.

Les données fournies dans le présent

manuel d'entretien peuvent faire l'objet

de modifications en vue de perfectionner

le produit.

Die

in

diesem

Wartungshandbuch

enthaltenen Spezifikationen können sich

zwecks Verbesserungen ändern.

SPECIFICATIONS AND PARTS ARE SUBJECT TO CHANGE FOR IMPROVEMENT

DVD AV Receiver and Digital Terrestrial TV Receiver

October 2004

SM0154

HTD-K185UK

A) HARDWARE

1. GENERAL DESCRIPTION

1.1 MT1379

The MT1379 Progressive Scan DVD-Player Combo Chip is a single-chip MPEG video

decoding chip that integrates audio/video stream data processing, TV encoder, four video

DACs with Macrovision, copy protection, DVD system navigation, system control and

housekeeping functions.

The features of this chip can be listed as follows;

General Features:

*Progressive scan DVD-player combo chip

*Integrated NTSC/PAL encoder,

*Built-in progressive video output

*DVD-Video, VCD 1.1, 2.0, and SVCD,

*Unified track buffer and A/V decoding buffer,

*Direct interface of 32-bit SDRAM,

*Servo controller and data channel processing.

Video Related Features:

*Macrovision 7.1 for NTSC/PAL interlaced video,

*Simultaneous composite video and S-video outputs, or composite and YUV outputs,

or composite and RGB outputs.

*8-bit CCIR 601 YUV 4:2:2 output.

* Decodes MPEG video and MPEG2 main profile at main level.

* Maximum input bit rate of 15Mbits/sec.

Audio Related Features:

*Dolby Digital (AC-3) and Dolby Pro Logic

*Dolby Digital S/PDIF digital audio output

*High-Definition Compatible Digital. (HDCD) decoding

*Dolby Digital Class A and HDCD certified

*SRS True Surround

*CD-DA

*MP3

1.2 Memory

SDRAM Memory Interface

The MT1379 provides a glueless 16-bit interface to DRAM memory devices used as

OSD, MPEG stream and video buffer memory for a DVD player. The maximum amount of

memory support is 16 MB of Synchronous DRAM (SDRAM). The memory interface is

configurable in depth to support 128-Mb addressing. The memory interface controls

access to both external SDRAM memories, which can be the sole unified external

read/write memory acting as program and data memory as well as various decoding and

display buffers.

1.3 Drive Interfaces

The MT1379 supports the DV34 interface, and other RF and servo interfaces used

by many types of DVD loaders. These interfaces meet the specifications of many DVD

loader manufacturers.

1.4 Front Panel

The front panel is based around a Futaba VFD and a common NEC front panel

controller chip, (uPD16311). The MT1379 controls the uPD16311 using several control

signals, (clock, data, chip select). The infrared remote control signal is passed directly to

the MT1379 for decoding.

1.5 Rear Panel

A typical rear panel is included in the reference design. This rear panel supports:

· Six channel or two channel audio outputs,

· Optical and coax SPDIF outputs,

· Composite, S-Video, and SCART outputs.

The six-video signals used to provide CVBS, S-Video, and RGB are generated by the

MT1379's internal video DAC, The video signals are buffered by external circuitry.

Six channel audio output by the MT1379 in the form of three I2S (or similar) data

streams. The S/PDIF serial stream is also generated by the MT1379 output by the rear

panel. The six channel audio DACs (AK4356, PCM1606) are used for six channel audio

output with MT1379, and similarly AK4382A, CS4392 Audio DACs are used for two

channel audio output with MT1379.

12-pin DDX board output jack gives out the amplified audio. Digital Audio is processed

in the DDX-8228 IC and then amplified in the DDX-2050 Power Amplifier ICs.

2. SYSTEM BLOCK DIAGRAM AND MT1379 PIN DECRIPTION

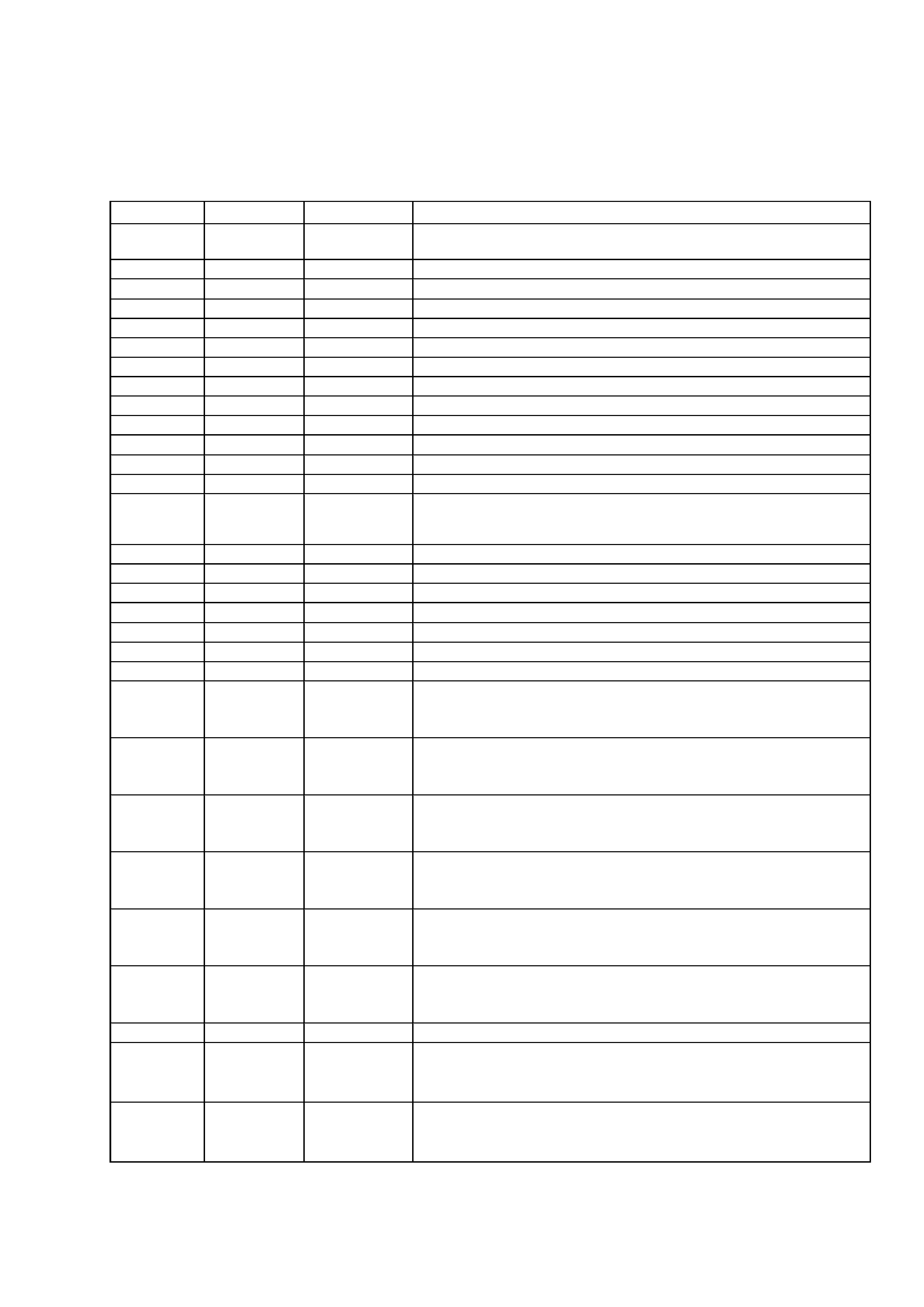

2.1 MT1379 Pin Description

Pin Number

Symbol

Type

Description

1

IREF

Analog Input

Current reference input. It generates reference current for data PLL. Connect

an external 100K resistor to this pin and PLLVSS.

2

PLLVSS

Ground

Ground pin for data PLL and related analog circuitry

3

LPIOP

Analog Output

Positive output of the low pass filter

4

LPION

Analog Output

Negative output of the low pass filter

5

LPFON

Analog output

Negative output of loop filter amplifier

6

LPFIP

Analog Input

Positive input of loop filter amplifier

7

LPFIN

Analog Input

Negative input of loop filter amplifier

8

LPFOP

Analog Output

Positive output of loop filter amplifier

9

JITFO

Analog Output

RF jitter meter output

10

JITFN

Analog Input

Negative input of the operation amplifier for RF jigger meter

11

PLLVDD3

Power

3.3V power pin for data PLL and related analog circuitry

12

FOO

Analog Output

Focus servo output. PDM output of focus servo compensator

13

TRO

Analog Output

Tracking servo output. PDM output of tracking servo compensator

14

TROPENPWM

Analog Output Tray open output, controlled by microcontroller. This is PWM output

for TRWMEN27hRW2=1 or is digital output for TRWMEN27hRW2=0

15

PWMOUT1

Analog Output

The 1st general PWM output

16

PWMOUT2

Analog Output

The 2nd general PWM output

17

DVDD2

Power

2.5V power pin for internal fully digital circuitry

18

DMO

Analog Output

Disk motor control output. PWM output

19

FMO

Analog Output

Feed motor control. PWM output

20

DVSS

Ground

Ground pin for internal fully digital circuitry

21

FG

Input ^1

Motor Hall sensor input

22

HIGHAO

Inout 2-16 MA,

SR PU

Microcontroller address 8

23

HIGHA1

Inout 2-16

MA, SR PU

Microcontroller address 9

24

HIGHA2

Inout 2-1 6MA,

SR PU

Microcontroller address 10

25

HIGHA3

Inout 2-16MA,

SR PU

Microcontroller address 11

26

HIGHA4

Inout 2-16MA,

SR PU

Microcontroller address 12

27

HIGHA5

Inout 2-16MA,

SR PU

Microcontroller address 13

28

DVSS

Ground

Ground pin for internal digital circuitry

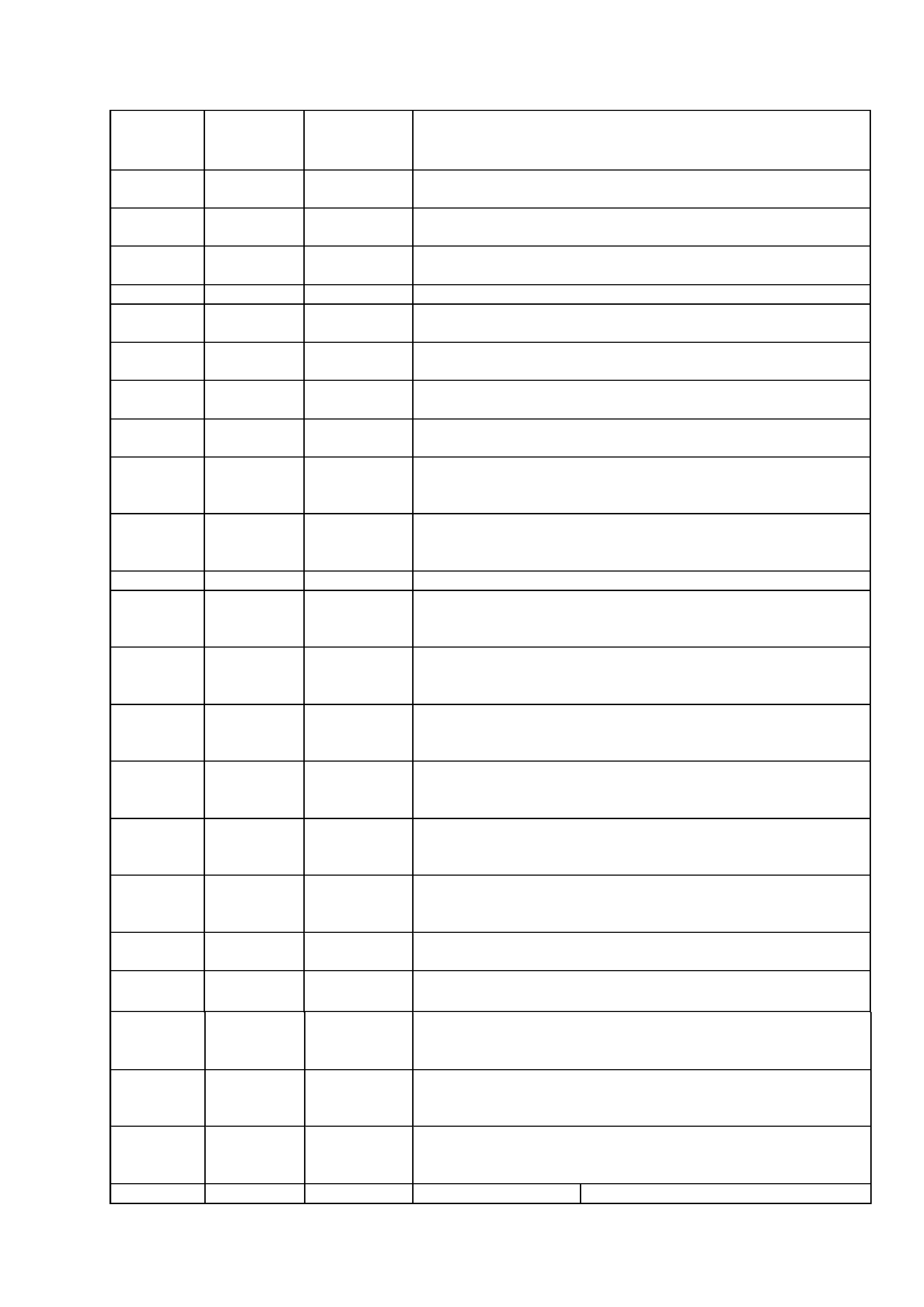

29

HIGHA6

Inout 2-16MA,

SR PU

Microcontroller address 14

30

HIGHA7

Inout 2-16MA,

SR PU

Microcontroller address 15

31

AD7

Inout 2-16MA,

SR

Microcontroller address/data 7

32

AD6

Inout 2-16MA,

SR

Microcontroller address/data 6

33

ADS

Inout 2-16MA,

SR

Microcontroller address/data 5

34

AD4

Inout 2-16MA,

SR

Microcontroller address/data 4

35

DVDD3

Power

3.3V power pin for internal digital circuitry

36

ADS

Inout 2-16MA,

SR

Microcontroller address/data 3

37

AD2

Inout 2-16MA,

SR

Microcontroller address/data 2

38

AD1

Inout 2-16MA,

SR

Microcontroller address/data 1

39

ADO

Inout 2-16MA,

SR

Microcontroller address/data 0

40

IOAO

Inout 2-16MA,

SR PU

Microcontroller address 0 / IO

41

IOA1

Inout 2-16MA,

SR PU

Microcontroller address 1 / IO

42

DVDD2

Power

2.5V power pin for internal digital circuitry

43

IOA2

Inout 2-16MA,

SR PU

Microcontroller address 2 / IO

44

Inout 2-16 MA,

SR PU

Microcontroller address 3 / IO

45

IOA4

Inout 2-16MA,

SR PU

Microcontroller address 4 / IO

46

IOA5

Inout 2-16MA,

SR PU

Microcontroller address 5 / IO

47

IOA6

Inout 2-16MA,

SR PU

Microcontroller address 6 / IO

48

IOA7

Inout 2-16MA,

SR PU

Microcontroller address 7 / IO

49

A16

Output

2-16MA, SR

Flash address 16

50

A17

Output

2-16MA, SR

Flash address 17

51

IOA18

Inout 2-16MA,

SR SMT

Flash address 18 /IO

52

IOA19

Inout 2-16MA,

SR SMT

Flash address 19 /IO

53

IOA20

Inout 2-16MA,

SR SMT

Flash address 20 / IO OR

Video in Data PortB 0

54

APLLVSS

Ground

Ground pin for audio clock

circuitry