CAUTION:

Before servicing this chassis, it is important that the service technician read the "Safety

Precautions" and "Product Safety Notices" in this service manual.

ATTENTION:

Avant d'effectuer l'entretien du châassis, le technicien doit lire les «Précautions de sécurité»

et les «Notices de sécurité du produit» présentés dans le présent manuel.

VORSICHT:

Vor Öffnen des Gehäuses hat der Service-Ingenieur die ,,Sicherheitshinweise" und ,,Hinweise

zur Produktsicherheit" in diesem Wartungshandbuch zu lesen.

SERVICE MANUAL

MANUEL D'ENTRETIEN

WARTUNGSHANDBUCH

Data

contained

within

this

Service

manual is subject to alteration for

improvement.

Les données fournies dans le présent

manuel d'entretien peuvent faire l'objet

de modifications en vue de perfectionner

le produit.

Die

in

diesem

Wartungshandbuch

enthaltenen Spezifikationen können sich

zwecks Verbesserungen ändern.

January 2001

COLOUR TELEVISION

C28WF530N

C28WF530NIRISH

C28WF532N

C28WF535N

C32WF535N

C32WF535NIRISH

CL28WF530AN

CL28WF535AN

CL32WF535AN

SM00031

SPECIFICATIONS AND PARTS ARE SUBJECT TO CHANGE FOR IMPROVEMENT

A20 service information

POWER SUPPLY

This chassis has two main power supplies.

The first, main constituent parts are I905 (VIPER 20/50), T901, rectifier diode D953, opto isolator I997 and

I943.

The second, main constituent parts are I900 (UC3844), Q903 (BUT12AF), Q904 (IRFS530A), T900,

rectifier diodes D955, D970, D977 & D925, opto isolator I999 and Q923.

First power supply

At switch on the mains is applied to the bridge rectifier D961, D962, D963, D964 unlike previous chassis's

there is not a large reservoir capacitor, it has been replaced by the network consisting of R909, C920,

D920, D921, C921, D931, C905, D922, C908, D923 and D924. These components have been added to

comply with HARMONIC legislation. The 375V dc output is applied to pin 2 of T901 (the primary winding)

via R980 a 1

fusible resistor. Pin 7 of T901 is connected to pin 3 of I905.

The IC has an internal current source derived from the high voltage input to start the oscillator, this internal

start up path is disconnected the voltage on the VDD pin 2 reaches 11V, this is generated by the secondary

winding between pins 4 & 5 of T901 and rectified by D992.

Pin 1has an R-C network connected to it for setting the switching frequency.

Pin 4 is the ground connection.

Pin 5 is the compensation input used to regulate the PWM output.

The main secondary winding (8V) of T901 is connected between pins 9+10 (ground) and 12+13, which is

connected to D953, smoothed by C914/C916.

R944 and R945 are used to set a reference level for the gate of I943 a programmable reference device.

The cathode of I943 is connected to pin 2 of I997 (opto isolator). Pin 1 of which is pulled up from the 8V via

R943. Pin 3 of I997 is connected to the primary side ground and pin 4 is connected to pin 5 of I905 forming

the control circuit.

The output from D953 is then filtered by L911/C959 this is the header voltage for I903 a 5v regulator for the

standby 5V used to supply the microprocessor and associated parts.

The MOSFET Q911 is controlled by the +17V generated by the second power supply (which is controlled

by the ON/OFF line) switches the 8V to the rest of the chassis to be used by I401, I501 etc. The switched

8V also used as the header voltage for a 5V regulator I904 used by I401, U101 etc.

Caution if test equipment is attached or removed from pin 3 of I905 while the set is

powered up I905 will be damaged!

Second power supply

The second power supply is used to generate the +B, +17V, -17V and a floating 14V for use by the DC to

DC converter which controls the final +B.

The same bridge rectifier and harmonic suppression circuitry as the first power supply. The 375V is then

applied to the collector of Q903 via the primary winding (pins 8 & 2) of T900. Initially the voltage on pin 7 of

I900 will rise to approximately 16V via R901, D905 and Q913. This allows the internal circuitry of I900 to

generate a sawtooth waveform at pin 4, from which a squarewave output is obtained at pin 6. This output is

applied to the gate of Q901, which turns on, and off, this alters the voltage on the emitter of Q903 causing

this device to turn on and off, generating the outputs in the secondary windings of T900.

When the 8V from the first power supply has stabilised and the microprocessor I003 has reset and taken

control of the ON/OFF line, the second power supply will be turned off and then turned back on in a

controlled manner at the correct time.

After initial power up I900 pin 7 is supplied from the bias winding (pin 4) of T900 via D916 for continued

operation.

A current sense circuit consisting of R956, R994, R995 and VR904 feeds back a voltage to pin 3 of I900,

MAX voltage approximately 0.8V. Should the applied voltage exceed the reference the pulse width is

limited from output pin 6. In this way Q903 is offered protection from changes in primary current.

A sense voltage from potential divider R992 and R950, is supplied to pin 2 of I900, this is then compared to

an internal reference voltage. If it exceeds the internal reference, the internal error amp will limit the output

from pin 6.

R911, R912, Q923 and I999 regulate the secondary voltages of T900. R911 and R912 sample the +B to

give a reference voltage to the gate of Q923.

I999 is dependent on the 8V from the first power supply to regulate the second power supply correctly, if

the 8V is missing the +B voltage will rise from approximately 170V to approximately 200V.

D955 rectifies the +B that is smoothed by C950.

D925 rectifies the audio +17V that is smoothed by C952.

D977 rectifies the audio -17V that is smoothed by C951.

DC to DC converter

The main constituent parts of the DC to DC converter are I902, Q927, L961, Q964 and I964.

NOTE the 0V (pin 5) of I902 is floating connected to the Source of the Mosfet Q927.

The UC3843 (I902) differs from the UC3844 (I900) only in the maximum duty cycle available.

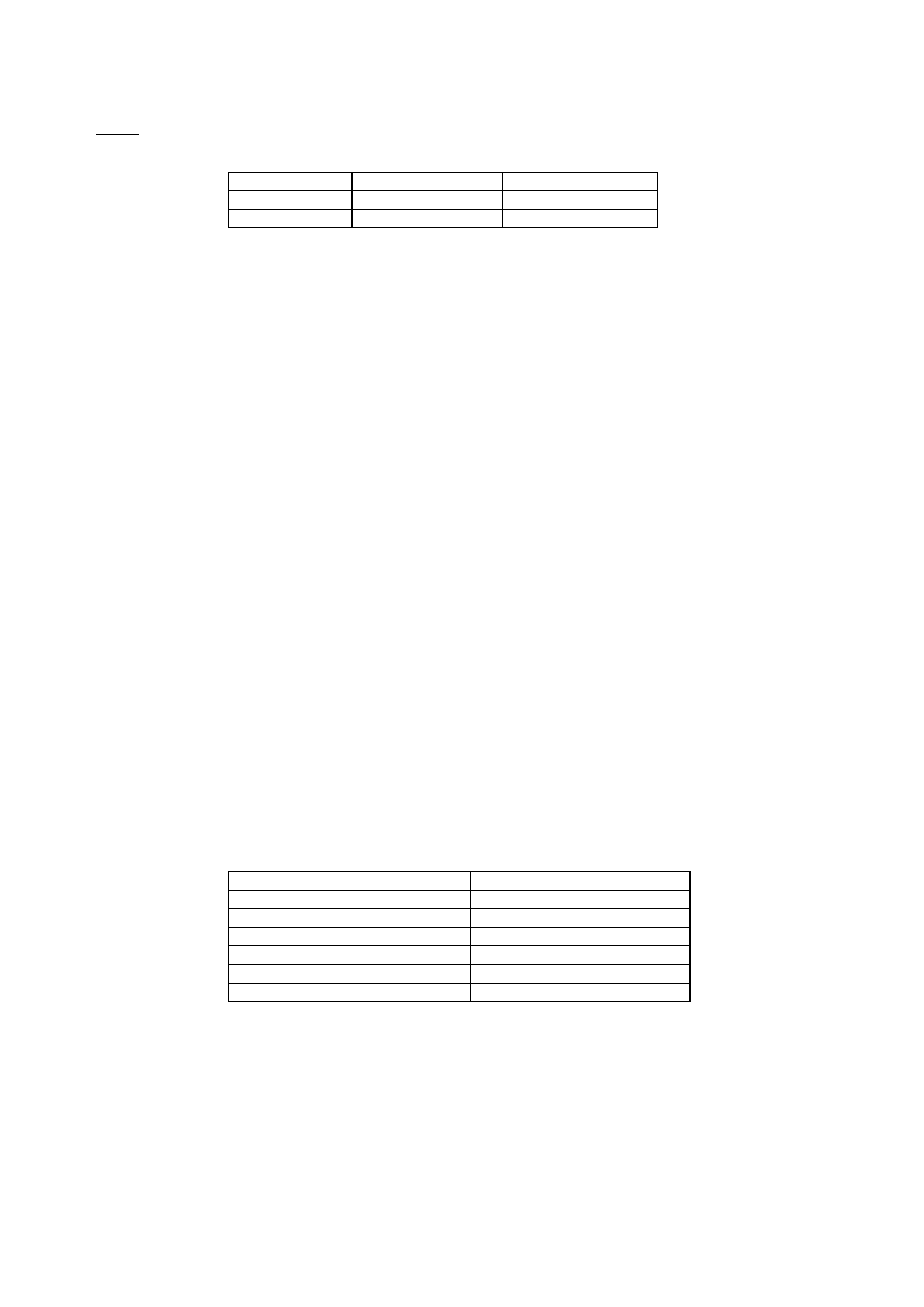

Device

Minimum duty cycle

Maximum duty cycle

UC3843

0%

100%

UC3844

0%

50%

The supply for pin 7 I902 is generated by the T900 winding between pins 12 + 10, when 9V is reached the

oscillator pin 4 will produce a sawtooth waveform, and pin 6 will output the PWM waveform for the gate of

the Mosfet Q927. The drain of Q927 is supplied by the +B from D955.

R968, R970 and R976 are used to sample the current, which is fed back to pin 3 I902.

L961 and C933 filter the final +B; R927 is used to supply a minimum load to ensure the continued correct

operation of the converter. The regulation is carried out by R958, VR964 and R960 sampling the final +B,

the slider of VR964 is connected to the gate of the programmable regulator Q964, the anode of which is

connected to the main STAR GROUND. The cathode is connected to the opto isolator I964 pin 2, pin 1 is

connected to the non switched 8V via R957. Pin 4 I964 is connected to the floating 0V and pin 5 is

connected to pin 1 I902, which controls the output PWM at pin 6.

Under extreme picture conditions i.e. very dark or bright pictures, the final +B will be altered slightly

automatically by the +B COMP circuit, the base of Q777 is connected to pin 4 T700 (FBT) via R776, R737.

R959, R967 and R771 are effectively in parallel with R960 via the collector / emitter of Q777 which

dependent on picture content adjusts the voltage on the gate of Q964.

The final +B is protected from excessive current due to a layer short within T700 or on one of it's secondary

windings by I902 the duty cycle/pulse width thus limiting the current available, when this happens the frame

output supply voltage drops sufficiently to turn off I601. The microprocessor will then turn the set into stand

by when no frame pulse is detected.

POWER GOOD

The power good signal supplied to the microprocessor I003 is a mains frequency squarewave of

approximately 3V3 amplitude. The base of Q922 is connected to the neutral side of the AC mains input via

R902, D933 (56V Zener) and D939. The collector of Q922 is connected to pin 2 of I998 (opto isolator); pin

1 is connected to a 5V-reference voltage generated by I900 at pin 8. I998 pin 3 is connected to STAR

GROUND and pin 4 to the power good line via R908. The power good line has a pull up resistor R020 to

the 3V3 line generated by I001.

PROTECTION

Pin 21 is the PROT SENSE port on the micro processor I003, it is pulled up to the 3V3 rail via R033, when

the PROT SENSE line is pulled low when the rail being protected fails the set will go into stand by.

Standard signal diodes are connected with their anodes to the prot sense line and their cathodes to the

individual supply voltages.

Diode CRN

Supply rail protected

D601

14V I601

D622

200V CRT base

D645

45V I601

D745

20V CRT base

D984

+17V audio

D995

+5V

For EHT over voltage protection, the potential divider R718/R749 & R719 samples the 200V supply for the

CRT base. The sampled voltage passes to the 36V Zener diode Z713, when the EHT rises sufficiently so

that Z713 conducts the high is applied to the gate of Q702 via R716 the SCR turns on pulling the prot

sense line low, putting the set into stand by.

The +B over current protection is described in the DC to DC converter section.

HORIZONTAL DEFLECTION

The horizontal drive signal is generated within I501by an internal Voltage Controlled Oscillator running at a

frequency of 25 MHz. This oscillator is stabilised to that frequency by using the 12MHz frequency of the

crystal oscillator as a reference. The horizontal output signal is generated by means of a second loop that

compares the phase of the internal oscillator signal with the phase of the incoming flyback pulse.

To obtain a smooth switch-on and switch-off behaviour of the horizontal output stage the horizontal drive

signal is switched-on and off via the soft-start/soft-stop procedure.

This function is realised by means of a variation of the TON of the horizontal drive pulse. When the soft-start

procedure is completed the horizontal output is gated with the flyback pulse so that the horizontal output

transistor cannot be switched-on during the flyback time.

Over voltage conditions (X-ray protection) can be detected via the EHT tracking pin.

The horizontal drive output pin 40 of I501 has an external pull up resistor to the 8V supply R533. The

output is applied to the base of Q701 via R707. The collector is supplied from the +B via R705 and the

primary of the drive transformer T702. The secondary of T702 drives the base of the line output transistor

Q751. The collector is supplied from the +B via R735, L700 and the primary of the flyback Transformer.

The horizontal feed back to I501 pin 41 is taken from the collector of Q751 by capacitive divider C748/C769

& C708, passed through the R/C network of R724 & C724/C723 to the 5V6 Zener diode Z704, which is

then clamped by diodes D713 & D714. It then passes through R765 to the base of Q711, the emitter of

which as a pull up resistor to the 8V R769, this output is the applied to pin 41 I501 via R768.

A sandcastle pulse is visible at pin 41 is internally generated by I501.

Pin 50 (EHTO) I501 is used in 2 ways the first for EHT compensation, and is connected to the ACL pin 4 of

T700 via R737 and R605. This is used to alter the frame amplitude when extremes of picture content are

reached (bright or dark) to reduce the visible breathing.

Secondly it is used by the microprocessor I003 pin 1 to turn off the horizontal drive at mains off, standby

and under fault conditions. A high is output from pin 1 (shutdown), applied to the base of Q 605 via R667.

Q605 turns on pulling the base of Q606 low, which turns on applying a high voltage to pin 50 I501 via R616

and D603.

The horizontal drive will be stopped when pin 50 I501 exceeds 3.9V

VERTICAL DEFLECTION

The vertical deflection output IC I601 (TDA8358J) is a differential current amplifier. I501 generates the

vertical drive pluses; C518 the vertical sawtooth capacitor is connected to pin 51 (VCS). The drive pulses

are output from I501 pins 46 (VDRB) and 47 (VDRA), to I601 pins 2 & 1 respectfully via R608 and R607.

The supply voltage to pin 3 is generated by the FBT, is output from pin 5 rectified by D708 and smoothed

by C726.

The flyback pulse generator supply voltage also comes from the FBT, from pin 8 is rectified by D604 and

smoothed by C616.

Pin

Description

1

Vertical input (positive)

2

Vertical input (negative)

3

Supply voltage

4

Vertical output voltage B

5

East-West input voltage (not used)

6

Vertical ground

7

East-West ground

8

East-West output voltage (not used)

9

Flyback supply voltage

10

Vertical output voltage A

11

Guard output voltage (not used)

12

Input measuring resistor

13

Input compensation current

The East-West amplifier within the TDA8358 is not used in this application.

EAST-WEST CORRECTION

The East-West correction parabola is output from pin 45 of I501 this is applied to the gate of Q631. The

source is connected to ground, and the drain is connected to the centre of the diode modulator (D706,

D707 and D711) via R741 and the East-West injection coil L751.

Microcontroller Section on the A20 Chassis

Introduction:

The main microcontroller on the A20 chassis is located at I003 (SDA555xfl). This is a 52-pin shrink-DIP

package. This device controls many of the other integrated circuits via dedicated input/output lines or the

I2C bus. This device also generates the RGB signals for the on-screen display (OSD) menus and the

teletext. The device acquires, decodes and displays teletext signals. This microcontroller has internal

program for storage of software code. The television stores all the necessary customer preferences and

operating settings in an on-board EEPROM (E2). This device can hold 2Kb of information for storing the

programme information (frequency, name, AV setting, etc.), factory alignment settings (geometry, white

balance, tuner AFC/AGC, etc.), service diagnostic errors and customer control settings (volume,

brightness, contrast, etc.). This device communicates with the main microcontroller via the I2C bus.

Main Microcontroller (I003)

Introduction

The SDA555xfl is a microcontroller based on the 8051 core from Infineon. It is capable of displaying menus

and teletext for 50Hz and 100Hz televisions. This device can acquire/decode and display pages of teletext

information in FLOF (FastText) and TOP (only in Germany/Switzerland/Austria) modes. The device

operates from a single 6MHz crystal and +3.3V and +2.5V supplies.

Description

Ground Connections

Pins 29 and 43 (VSS) are the ground connections for the digital parts of the device.

Pins 14 and 36 (VSSA) are the ground connections for the analogue parts of the device.

Supply Connections

Pins 11, 30 and 44 (VDD3.3) are the +3.3V supply for the microcontroller peripheral parts. The 3V3 supply

is derived from the +5Vstandby supply by I001.

Pins 9 and 42 (VDD2.5) are the +2.5V supply for microprocessor core. The 2.5V supply is derived from the

3V3 supply D011.

Pins 13 and 37 (VDDA2.5) are the +2.5V analogue supply voltage pins for the ADC of the microcontroller.

This supply comes from the same supply as the 2.5V core supply, through L003.

Crystal Oscillator Connections

Pins 34 and 35 are the 6MHz crystal oscillator connections for the microcontroller.

Reset Connection

Pin 33 is the active low RESET input of the microcontroller. This input is normally high under operating

conditions, but changes state when the standby +3.3V power supply is below a threshold. In this

circumstance, the reset IC (I007) pulls pin 33 low until the input of it is above this threshold. The diode

(D015) ensures that the capacitor (C020) discharges quickly when the standby supply falls, so that the

reset operates quickly. The capacitor (C020) charges up slowly when the standby supply is restored,

ensuring that there is a reset delay.

Infra-red (IR) Receiver Input

Pin 24 is the IR receiver's filtered output. This input from the IR receiver (IR01) consists of PWM pulses

between 0V and +3.3V. These pulses are decoded by the microcontroller. The Red LED on the front of the

TV will briefly flash when a valid command has been received and decoded.