TS912

INPUT/OUTPUT RAIL TO RAIL

DUAL CMOS OPERATIONAL AMPLIFIER

March 1996

.

RAIL TO RAIL INPUT AND OUTPUT

VOLTAGE RANGES

.

SINGLE (OR DUAL) SUPPLY OPERATION

FROM 2.7V TO 16V (

±1.35V to ±8V)

.

EXTREMELY LOW INPUT BIAS CURRENT :

1pA TYP

.

LOW INPUT OFFSET VOLTAGE :

2mV max.

.

SPECIFIED FOR 600

AND 100 LOADS

.

LOW SUPPLY CURRENT : 400

µA/Ampli

.

SPEED : 1.4MHz - 1.3V/

µs

.

ESD TOLERANCE : 3KV

.

LATCH-UP IMMUNITY

.

SPICE MACROMODEL INCLUDED IN THIS

SPECIFICATION

1

2

3

45

6

7

8

-

+

-

+

Inverting Input 1

Output 1

Non-inverting Input 1

VCC

VCC +

Output 2

Inverting Inpu t 2

Non-inverting Input 2

PIN CONNECTIONS (top view)

DESCRIPTION

The TS912 is a RAIL TO RAIL dual CMOS opera-

tional amplifier designed to operate with single or

dual supply voltage.

The input voltage range Vicm includes the two

supply rails VCC

+ and VCC-.

The output reaches :

· V

CC

- +50mV

VCC

+ -50mV

with RL = 10k

· V

CC

- +650mV VCC+ -650mV with RL = 600

This product offers a broad supply voltage operat-

ing range from 2.7V to 16V, a supply current of only

400

µA/amp (VCC = 10V) and a high output current

capability fixed by an internal limitation circuit :

Isource = 65mA - Isink = 75mA

ORDER CODES

Part Number

Temperature Range

Package

ND

TS912I/AI/BI

-40, +125

oC

··

N

DIP8

(Plastic Package)

D

SO8

(Plastic Micropackage)

1/10

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Value

Unit

VCC

Supply Voltage - (note 1)

18

V

Vid

Differential Input Voltage - (note 2)

±18

V

Vi

Input Voltage - (note 3)

-0.3 to 18

V

Iin

Current on Inputs

±50

mA

Io

Current on Outputs

±130

mA

Toper

Operating Free Air Temperature Range

TS912I/AI/BI

-40 to +125

oC

Tstg

Storage Temperature

-65 to +150

oC

Notes :

1. All voltage values, except differential voltage are with respect to network ground terminal.

2. Differential voltages are the non-inverting input terminal with respect to the inverting input terminal.

3. The magnitude of input and output voltages must never exceed VCC

+ +0.3V.

OPERATING CONDITIONS

Symbol

Parameter

Value

Unit

VCC

Supply Voltage

2.7 to 16

V

Vicm

Common Mode Input Voltage Range

VCC

- -0.2 to VCC++0.2

V

Non-inverting

Input

Inverting

Input

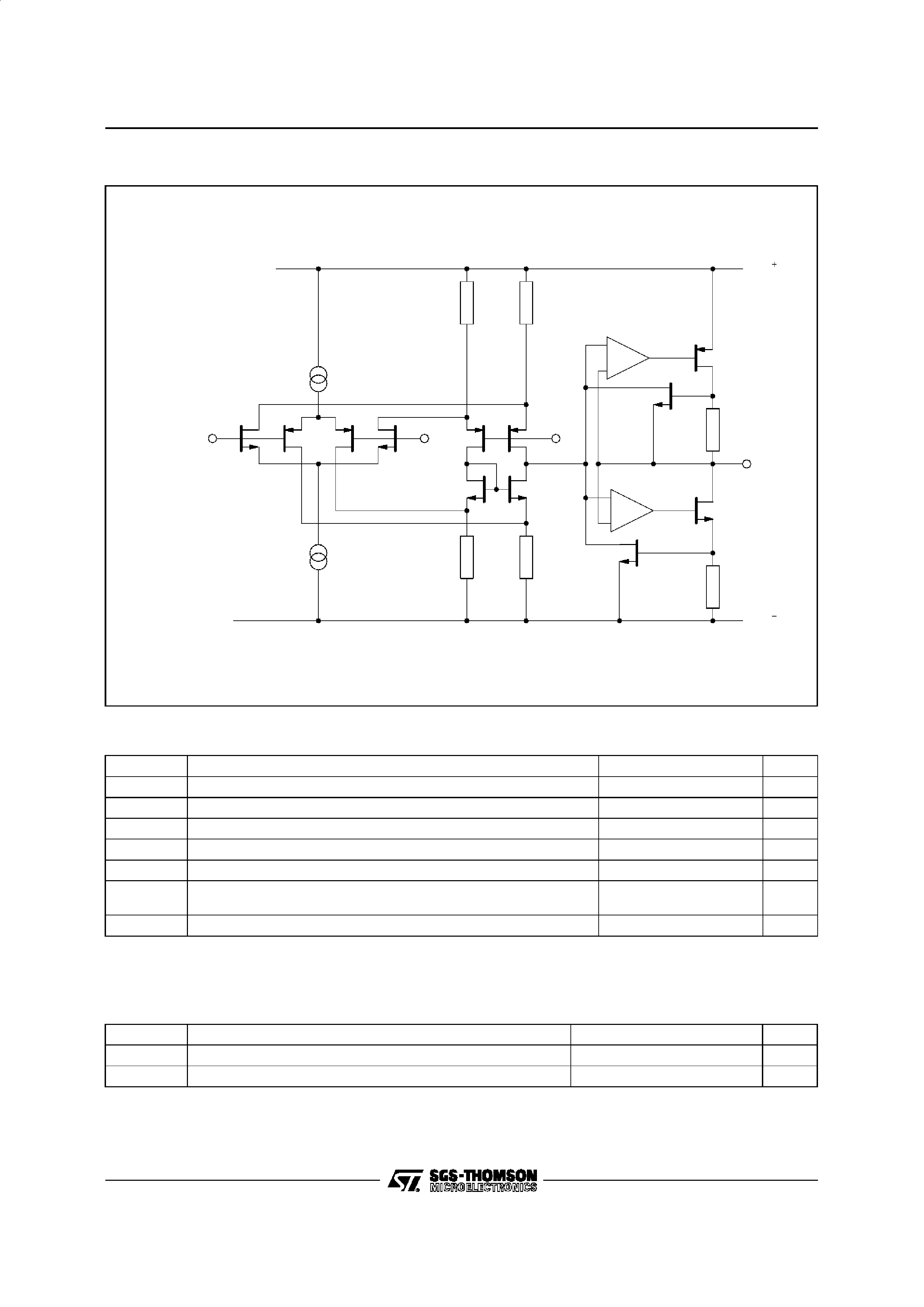

Inte rnal

Vre f

Output

VCC

VCC

SCHEMATIC DIAGRAM (1/2 TS912)

TS912

2/10

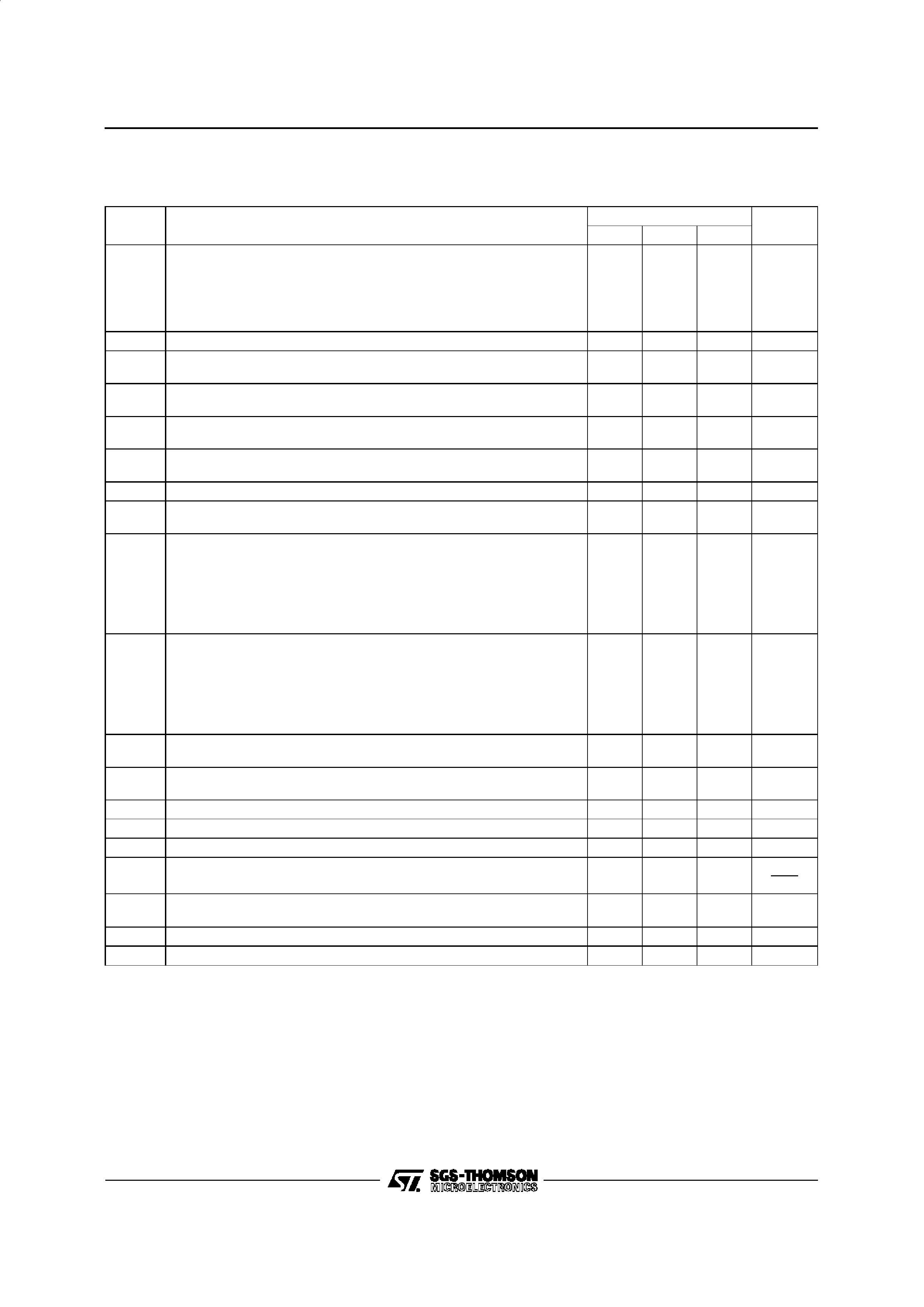

ELECTRICAL CHARACTERISTICS

VCC

+ = 10V, VCC- =0V, RL,CL connected to VCC/2, Tamb =25oC (unless otherwise specified)

Symbol

Parameter

TS912I/AI/BI

Unit

Min.

Typ.

Max.

Vio

Input Offset Voltage (Vic =Vo =VCC/2)

TS912

TS912A

TS912B

Tmin.

Tamb Tmax.

TS912

TS912A

TS912B

10

5

2

12

7

3

mV

DVio

Input Offset Voltage Drift

5

µV/oC

Iio

Input Offset Current - (note 1)

Tmin.

Tamb Tmax.

1

100

200

pA

Iib

Input Bias Current - (note 1)

Tmin.

Tamb Tmax.

1

150

300

pA

ICC

Supply Current (per amplifier, AVCL = 1, no load)

Tmin.

Tamb Tmax.

400

600

700

µA

CMR

Common Mode Rejection Ratio

Vic = 3 to 7V, Vo =5V

Vic = 0 to 10V, Vo =5V

60

50

90

75

dB

SVR

Supply Voltage Rejection Ratio (VCC

+ = 5 to 10V, VO =VCC /2)

60

90

dB

Avd

Large Signal Voltage Gain (RL =10k

,VO = 2.5V to 7.5V)

Tmin.

Tamb Tmax.

20

15

60

V/mV

VOH

High Level Output Voltage (Vid = 1V)

RL = 100k

RL =10k

RL = 600

RL = 100

Tmin.

Tamb Tmax.

RL =10k

RL = 600

9.95

9.85

9

9.8

8.8

9.95

9.35

7.8

V

VOL

Low Level Output Voltage (Vid = -1V)

RL = 100k

RL =10k

RL = 600

RL = 100

Tmin.

Tamb Tmax.

RL =10k

RL = 600

50

650

2300

50

150

800

150

900

mV

Io

Output Short Circuit Current (Vid =

±1V)

Source

(Vo =VCC

-

)

Sink

(Vo =VCC

+)

45

50

65

75

mA

GBP

Gain Bandwidth Product

(AVCL = 100, RL =10k

,CL = 100pF, f = 100kHz)

1.4

MHz

SR

+

Slew Rate (AVCL =1, RL =10k

,CL = 100pF, Vi = 2.5V to 7.5V)

1.3

V/

µs

SR

-

Slew Rate (AVCL =1, RL =10k

,CL = 100pF, Vi = 2.5V to 7.5V)

0.8

V/

µs

m

Phase Margin

40

Degrees

en

Equivalent Input Noise Voltage (Rs = 100

, f = 1kHz)

30

nV

Hz

THD

Total Harmonic Distortion

(AVCL =1, RL =10k

,CL = 100pF, VO = 4.75V to 5.25V, f = 1kHz)

0.024

%

Cin

Input Capacitance

1.5

pF

VO1/VO2

Channel Separation (f = 1kHz)

120

dB

Note 1 : Maximum values including unavoidable inaccuracies of the industrial test.

TS912

3/10

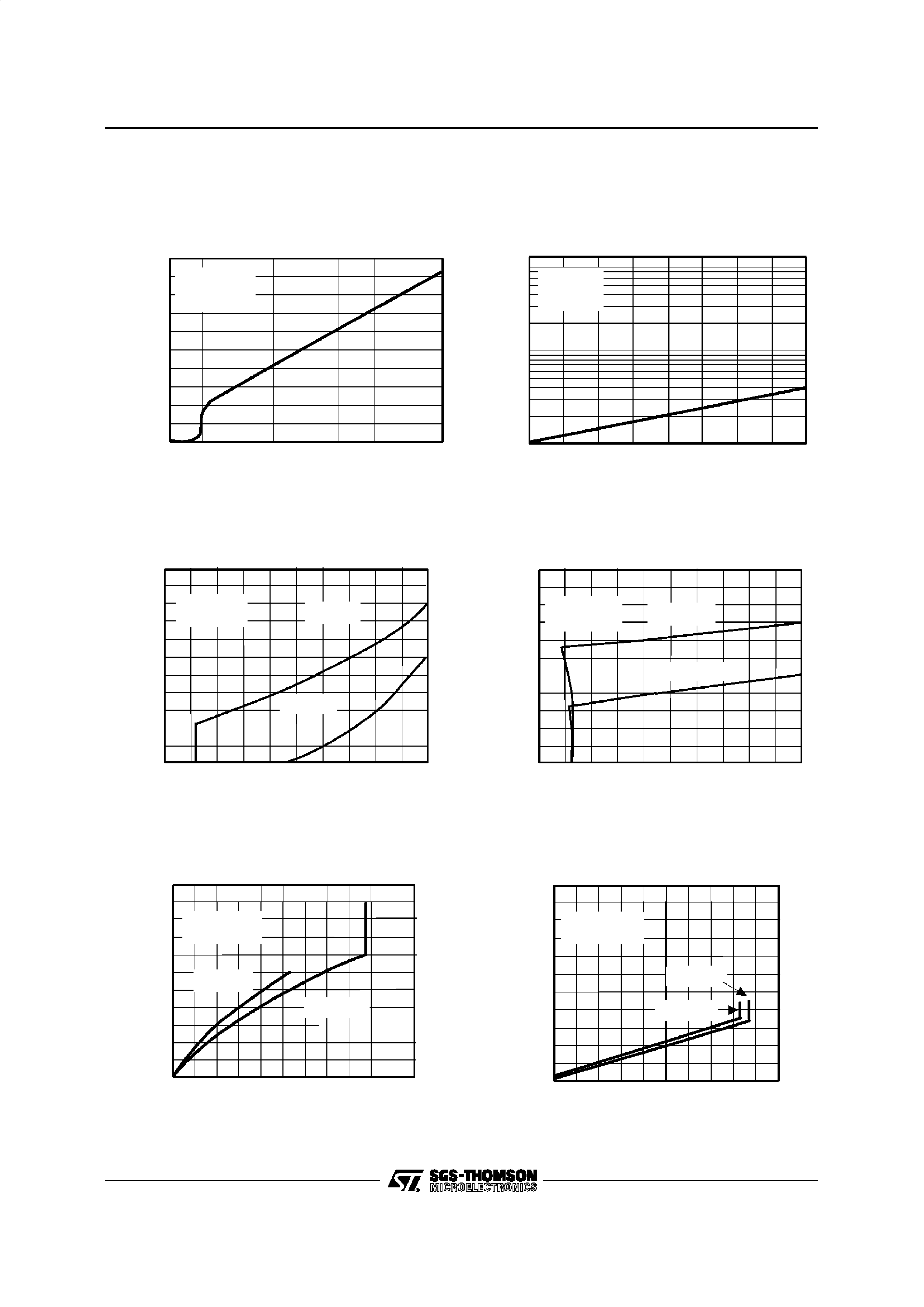

TYPICAL CHARACTERISTICS

CC

S UPP LY VOLTAGE, V

(V)

04812

16

T= 25 C

A= 1

V= V

/ 2

amb

VC L

OCC

CC

µ

SUPPLY

CURRENT,

I

(

A)

600

500

400

300

200

100

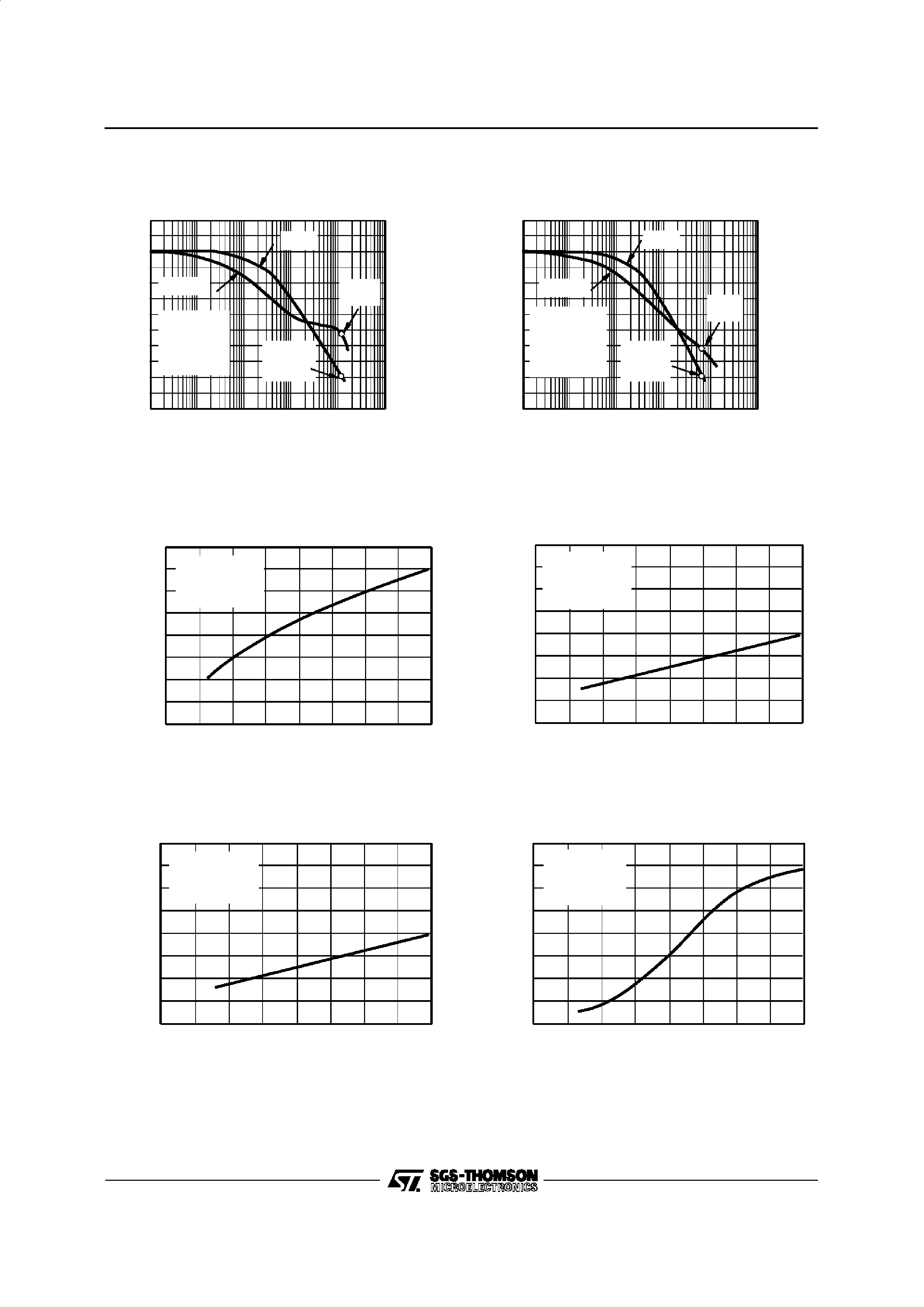

Figure 1 : Supply Current (each amplifier)

versus Supply Voltage

25

50

75

10 0

125

INPUT

BIAS

CURRENT,

I

(pA)

ib

V

= 10V

V= 5V

No load

CC

i

10 0

10

1

amb

TEMPERATURE, T

( C)

Figure 2 : Input Bias Current versus Temperature

1

14

28

42

56

70

OUTPUT

VOLTAGE,

V

(V)

OL

amb

id

T= 25 C

V

= -100mV

V

= +5V

CC

V

= +3V

CC

0

OL

OUTP UT CURRENT, I

(mA)

2

3

4

5

Figure 4a : Low Level Output Voltage versus

Low Level Output Current

2

OUTPUT

VOLTAGE,

V

(V)

OL

amb

id

T= 25 C

V

= -100mV

0

V= 1 0V

CC

V

= 16V

CC

OL

O UTPUT CURRENT, I

(mA)

4

6

8

10

14

28

42

56

70

Figure 4b : Low Level Output Voltage versus

Low Level Output Current

5

-70

-56

-42

-28

-14

0

OUTPUT

VOLTAGE,

V

(V)

OH

amb

id

T= 25 C

V

= 100mV

V

= +5V

CC

V

= +3 V

CC

4

3

2

1

0

OH

OUTPUT CURRENT, I

(mA)

Figure 3a : High Level Output Voltage versus

High Level Output Current

4

0

OUTPUT

VOLTAGE,

V

(V)

OH

V

= +16V

CC

V

= +10V

CC

OH

OUTP UT CURRENT, I

(mA)

12

8

20

16

-70

-56

-42

-28

-14

0

amb

id

T= 25 C

V

= 100mV

Figure 3b : High Level Output Voltage versus

High Level Output Current

TS912

4/10

50

40

30

20

10

0

-10

GAIN

(dB)

PHASE

(Degrees)

0

45

90

135

180

FR EQUENCY, f (Hz)

PHASE

GAIN

Pha s e

Ma rgin

Ga in

Ba ndwidth

P roduct

6

10

10

23

10

4

10

5

10

7

10

T= 25 C

V

= 10V

R

= 10k

C

= 100pF

A

= 100

amb

CC

L

L

VCL

Figure 5a : Open Loop Frequency Response

and Phase Shift

50

40

30

20

10

0

-

10

GAIN

(dB)

PHASE

(Degrees)

0

45

90

135

180

FREQUENCY, f (Hz)

P HASE

GAIN

Phas e

Margin

Ga in

Ba ndwidth

P roduct

6

10

10

23

10

4

10

5

10

7

10

T= 25 C

V= 1 0V

R

= 600

C

= 100 pF

A

= 100

amb

CC

L

L

VCL

Figure 5b : Open Loop Frequency Response

and Phase Shift

SUP P LY VOLTAGE, V

(V)

CC

04

8

12

16

1800

GAIN

BANDW.

PROD.,

GBP

(kHz)

T= 25 C

R

= 10k

C = 100pF

amb

L

L

1400

1000

600

200

Figure 6a : Gain Bandwidth Product versus

Supply Voltage

S UP P LY VOLTAGE, V

(V)

CC

04

8

12

16

GAIN

BANDW.

PROD.,

GBP

(kHz)

T= 25 C

R

= 600

C = 100pF

amb

L

L

180 0

14 00

1 000

600

20 0

Figure 6b : Gain bandwidth Product versus

Supply Voltage

S UP PLY VOLTAGE , V

(V)

CC

04

8

12

16

60

50

40

30

20

PHASE

MARGIN,

m

(Degrees)

T= 25 C

R

= 10k

C = 10 0pF

amb

L

L

Figure 7a : Phase Margin versus Supply Voltage

S UP P LY VOLTAGE, V

(V)

CC

04

8

12

16

60

50

40

30

20

PHASE

MARGIN,

m

(Degrees)

T= 25 C

R= 6 00

C = 1 00pF

amb

L

L

Figure 7b : Phase Margin versus Supply Voltage

TS912

5/10